- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN9117-MD (STANDARD MICROSYSTEMS CORP) HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | LAN9117-MD |

| 廠商: | STANDARD MICROSYSTEMS CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| 中文描述: | 1 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁數(shù): | 41/131頁 |

| 文件大小: | 1531K |

| 代理商: | LAN9117-MD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁

High Performance Single-Chip 10/100 Non-PCI Ethernet Controller

Datasheet

SMSC LAN9117

41

Revision 1.1 (05-17-05)

DATASHEET

3.10.3.2

Energy Detect Power-Down

This power-down mode is activated by setting the Phy register bit 17.13 to 1. Please refer to

Section

5.5.8, "Mode Control/Status," on page 111

for additional information on this register. In this mode when

no energy is present on the line, the PHY is powered down, with th exception of the management

interface, the SQUELCH circuit and the ENERGYON logic. The ENERGYON logic is used to detect

the presence of valid energy from 100Base-TX, 10Base-T, or Auto-negotiation signals

In this mode, when the ENERGYON signal is low, the PHY is powered-down, and nothing is

transmitted. When energy is received - link pulses or packets - the ENERGYON signal goes high, and

the PHY powers-up. It automatically resets itself into the state it had prior to power-down, and asserts

the INT7.1 bit of the register defined in

Section 5.5.11, "Interrupt Source Flag," on page 113

. If the

ENERGYON interrupt is enabled, this event will cause an interrupt to the host. The first and possibly

the second packet to activate ENERGYON may be lost.

When 17.13 is low, energy detect power-down is disabled.

3.11

Detailed Reset Description

The LAN9117 has five reset sources:

■

Power-On Reset (POR)

■

Hardware Reset Input Pin (nRESET)

■

Soft Reset (SRST)

■

PHY Soft Reset via PMT_CTRL bit 10 (PHY_RST)

■

PHY Soft Reset via PHY Basic Control Register (PHY REG 0.15)

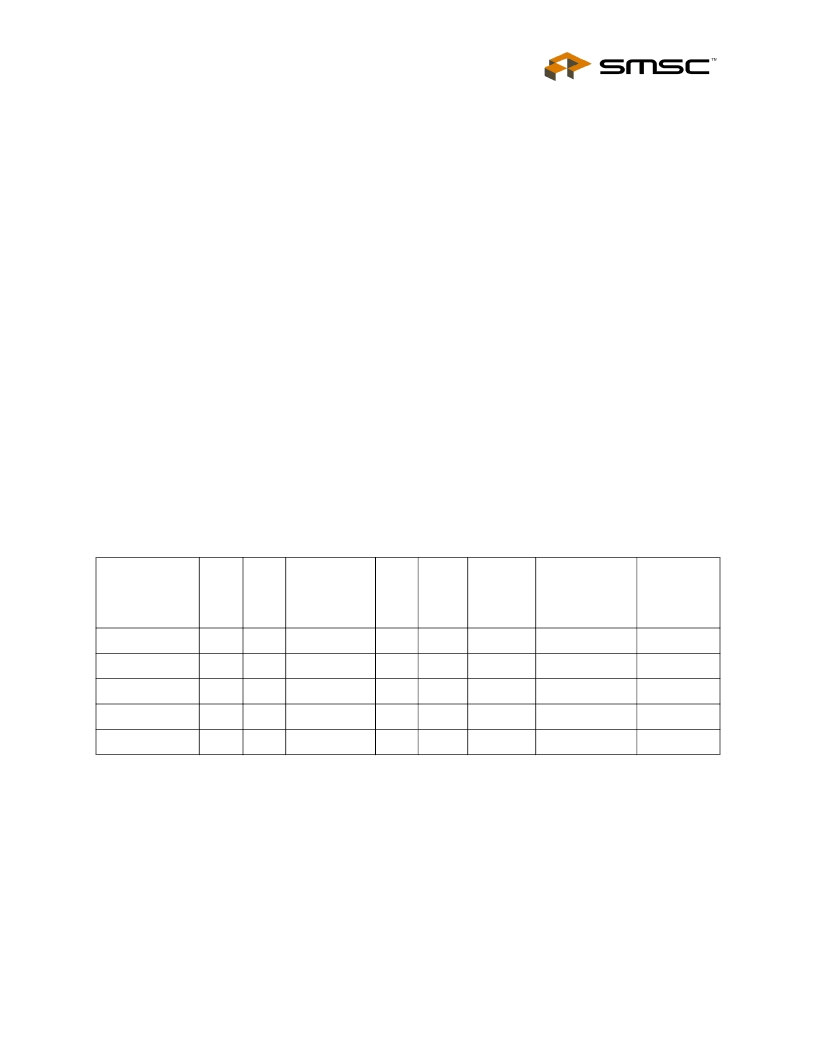

Table 3.10

shows the effect of the various reset sources on the LAN9117's circuitry.

Note 3.10

After any PHY reset, the application must wait until the “Link Status” bit in the PHY’s “Basic

Status Register” (PHY Reg. 1.2) is set before attempting to transmit or receive data.

Note 3.11

After a POR, nRESET or SRST, the LAN9117 will automatically check for the presence of

an external EEPROM. After any of these resets the application must verify that the EPC

Busy Bit (E2P_CMD, bit 31) is cleared before attempting to access the EEPROM, or

change the function of the GPO/GPIO signals, or before modifying the ADDRH or ADDRL

registers in the MAC.

Note 3.12

HBI - “Host Bus Interface”, NASR - Not affected by software reset

Table 3.10 PHY Reset Sources and Effected Circuitry

RESET

SOURCE

PLL

HBI

Note

3.12

NASR

REGISTERS

Note 3.12

MIL

MAC

PHY

Note 3.10

EEPROM MAC

ADDR.

RELOAD

Note 3.11

CONFIG.

STRAPS

LATCHED

POR

X

X

X

X

X

X

X

X

nRESET

X

X

X

X

X

X

X

X

SRST

X

X

X

X

PHY_RST

X

PHY REG 0.15

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN9117-MT | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| LAN9118 | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

| LAN9118-MD | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

| LAN9118-MT | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

| LAN91C100-FD-SS | FEAST Fast Ethernet Controller with Full Duplex Capability |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN9117-MT | 功能描述:以太網(wǎng) IC HiPerfrm Sngl-Chip 10/100 Ethrnt RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN9118 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single-Chip 10/100 Non-PCI Ethernet Controller |

| LAN9118_05 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single-Chip 10/100 Non-PCI Ethernet Controller |

| LAN9118_07 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single-Chip 10/100 Non-PCI Ethernet Controller |

| LAN9118-MD | 功能描述:以太網(wǎng) IC HiPerfrm Sngl-Chip 10/100 Ethrnt RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。