- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN83C185-JT (STANDARD MICROSYSTEMS CORP) HIGH PERFORMANCE SINGLE CHIP LOW POWER 10/100 ETHERNET PHYSICAL LAYER TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號(hào): | LAN83C185-JT |

| 廠商: | STANDARD MICROSYSTEMS CORP |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | HIGH PERFORMANCE SINGLE CHIP LOW POWER 10/100 ETHERNET PHYSICAL LAYER TRANSCEIVER |

| 中文描述: | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, TQFP-64 |

| 文件頁數(shù): | 19/61頁 |

| 文件大?。?/td> | 459K |

| 代理商: | LAN83C185-JT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

High Performance Single Chip Low Power 10/100 Ethernet Physical Layer Transceiver (PHY)

Datasheet

SMSC LAN83C185

19

Rev. 0.8 (11-16-04)

DATASHEET

4.2.3

Scrambling

Repeated data patterns (especially the IDLE code-group) can have power spectral densities with large

narrow-band peaks. Scrambling the data helps eliminate these peaks and spread the signal power

more uniformly over the entire channel bandwidth. This uniform spectral density is required by FCC

regulations to prevent excessive EMI from being radiated by the physical wiring.

The seed for the scrambler is generated from the PHY address, PHYAD[4:0], ensuring that in multiple-

PHY applications, such as repeaters or switches, each PHY will have its own scrambler sequence.

The scrambler also performs the Parallel In Serial Out conversion (PISO) of the data.

4.2.4

NRZI and MLT3 Encoding

The scrambler block passes the 5-bit wide parallel data to the NRZI converter where it becomes a

serial 125MHz NRZI data stream. The NRZI is encoded to MLT-3. MLT3 is a tri-level code where a

change in the logic level represents a code bit “1” and the logic output remaining at the same level

represents a code bit “0”.

4.2.5

100M Transmit Driver

The MLT3 data is then passed to the analog transmitter, which launches the differential MLT-3 signal,

on outputs TXP and TXN, to the twisted pair media via a 1:1 ratio isolation transformer. The 10Base-

T and 100Base-TX signals pass through the same transformer so that common “magnetics” can be

used for both. The transmitter drives into the 100

impedance of the CAT-5 cable. Cable termination

and impedance matching require external components.

4.2.6

100M Phase Lock Loop (PLL)

The 100M PLL locks onto reference clock and generates the 125MHz clock used to drive the 125 MHz

logic and the 100Base-Tx Transmitter.

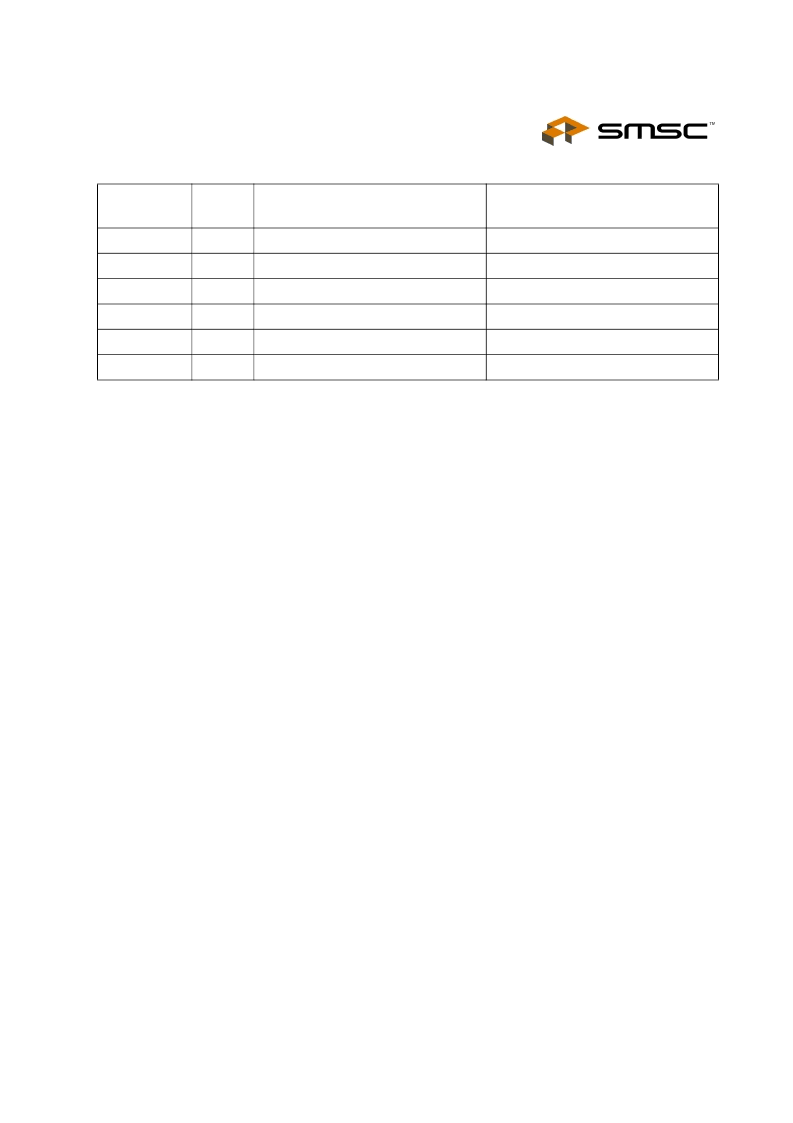

00010

V

INVALID, RX_ER if during RX_DV

INVALID

00011

V

INVALID, RX_ER if during RX_DV

INVALID

00101

V

INVALID, RX_ER if during RX_DV

INVALID

01000

V

INVALID, RX_ER if during RX_DV

INVALID

01100

V

INVALID, RX_ER if during RX_DV

INVALID

10000

V

INVALID, RX_ER if during RX_DV

INVALID

Table 4.1 4B/5B Code Table (continued)

CODE

GROUP

SYM

RECEIVER

INTERPRETATION

TRANSMITTER

INTERPRETATION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN8700 | 【15kV ESD Protected MII/RMII Fast-Ethernet PHY with HP Auto-MDIX and SMSC flexPWR TM in a Small Footprint |

| LAN9115 | HIGHLY EFFICIENT SINGLE - CHIP 10/100 NON PCI ETHERNET CONTROLLER |

| LAN9115-MD | HIGHLY EFFICIENT SINGLE - CHIP 10/100 NON PCI ETHERNET CONTROLLER |

| LAN9115-MT | HIGHLY EFFICIENT SINGLE - CHIP 10/100 NON PCI ETHERNET CONTROLLER |

| LAN9116 | Highly Efficient Single-Chip 10/100 Non-PCI Ethernet Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN83C795QFP WAF | 制造商:SMSC 功能描述: |

| LAN8700 | 制造商:SMSC 制造商全稱:SMSC 功能描述:【15kV ESD Protected MII/RMII Fast-Ethernet PHY with HP Auto-MDIX and SMSC flexPWR TM in a Small Footprint |

| LAN8700AEZG | 制造商:SMSC 功能描述: |

| LAN8700-AEZG | 功能描述:以太網(wǎng) IC HIPERFRM ETHRNT PHY RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN8700C-AEZG | 功能描述:以太網(wǎng) IC IC w/HP Auto-MDIX Embedded Ethernet RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。