- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360868 > IP100 PCI 10/100M Single Chip Ethernet Controller PDF資料下載

參數(shù)資料

| 型號(hào): | IP100 |

| 英文描述: | PCI 10/100M Single Chip Ethernet Controller |

| 中文描述: | 單芯片的PCI個(gè)10/100M以太網(wǎng)控制器 |

| 文件頁(yè)數(shù): | 46/92頁(yè) |

| 文件大小: | 2801K |

| 代理商: | IP100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

IP100

Copyright

2003, IC Plus Corp.

All rights reserved.

Preliminary, Specification subject to change without notice.

46/92

IP100-DS-R03

May 27, 2003

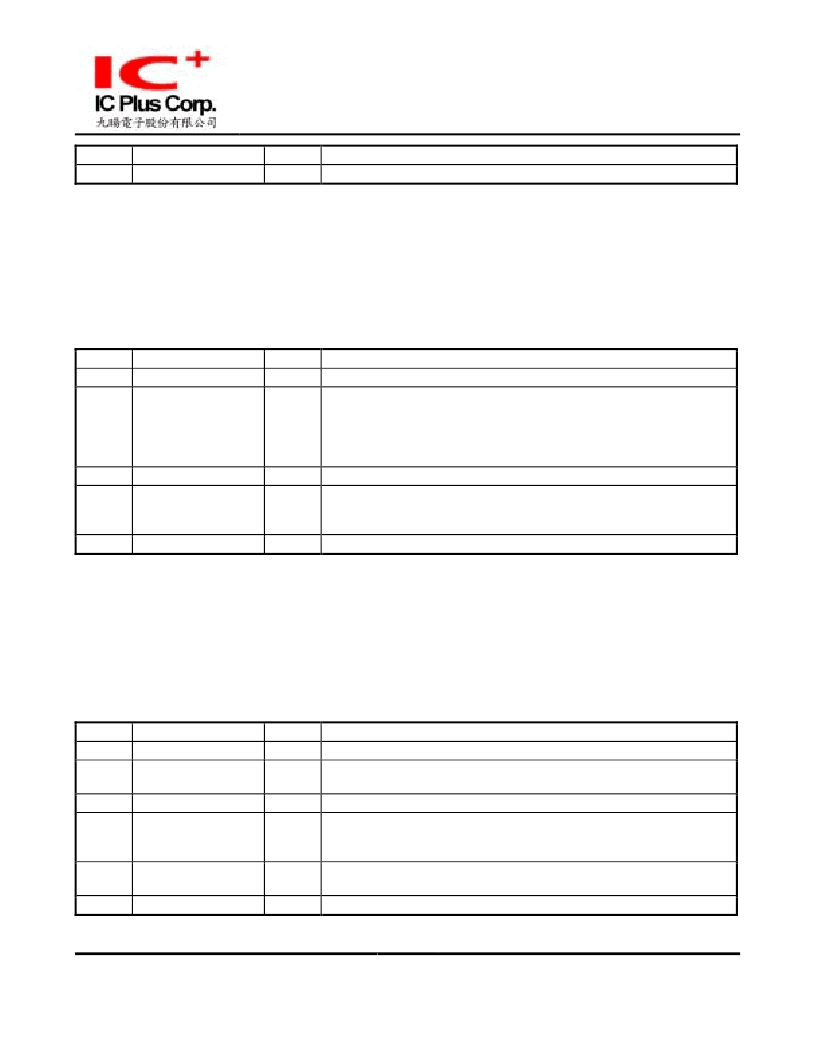

BIT

31..16

BIT NAME

Reserved

R/W

N/A

BIT DESCRIPTION

Reserved for future use.

10.4.11 FunctionEvent

Class............................. LAN I/O Registers, CardBus Status Change

Base Address ............... IoBaseAddress register value

Address Offset .............. 0x24

Default Value ................ 0x00000000

Width ............................ 32 bits

FunctionEvent contains the bits which can be used to generate status change interrupts, depending upon the

setting of the FunctionEventMask register. This register is disabled when the CardBus bit of AsicCtrl is low.

BIT

BIT NAME

R/W

3..0

Reserved

N/A

Reserved for future use.

4

GWAKE

R/W

GWAKE. GWAKE is a logic 1 and remains a logic 1 when the

GWAKE bit of the FunctionPresentState register is a logic 1.

GWAKE is cleared by writing a logic 1 to GWAKE. Writing a logic 1

to GWAKE also clears the PmeStatus bit of the PowerMgmtCtrl

register.

14..5

Reserved

N/A

Reserved for future use.

15

INTR

R/W

INTR. INTR is a logic 1 whenever an interrupt is pending regardless

of the INTR bit in the FunctionEventMask register. INTR is cleared

by writing a logic 1 to INTR.

31..16

Reserved

N/A

Reserved for future use.

10.4.12 FunctionEventMask

Class............................. LAN I/O Registers, CardBus Status Change

Base Address ............... IoBaseAddress register value

Address Offset .............. 0x28

Default Value ................ 0x00000000

Width ............................ 32 bits

FunctionEventMask masks the FunctionEvent register. This register is disabled when the CardBus bit of AsicCtrl

is low.

BIT

BIT NAME

R/W

3..0

Reserved

N/A

Reserved for future use.

4

GWAKE

R/W

GWAKE. If GWAKE is a logic 1, and WKUP is a logic 1 the GWAKE

bit of the FunctionEvent register may assert the CSTSCHGN signal.

13..5

Reserved

N/A

Reserved for future use.

14

WKUP

R/W

WKUP. If WKUP is a logic 1, all events (WriteProtect, Ready/Busy,

BatterryVoltageDetect, and GWAKE) may assert the CSTSCHGN

signal.

15

INTR

R/W

INTR. If INTR is a logic 1, setting the INTR bit of the FunctionEvent

register will assert the INTAN.

31..16

Reserved

N/A

Reserved for future use.

BIT DESCRIPTION

BIT DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP101 | PHY 10/100M Single Chip Fast Ethernet Transceiver |

| IP1060AD | Analog IC |

| IP1060AJ | Voltage-Mode SMPS Controller |

| IP1060AN | Analog IC |

| IP1060BJ | Voltage-Mode SMPS Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IP1000A | 制造商:IC PLUS 功能描述:IP1000A |

| IP1000ALF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

| IP1000ALF-DS-R01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

| IP1000ALF-DS-R02 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

| IP1000ALF-DS-R03 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。