- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1924 > IDT88P8342BHI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF資料下載

參數(shù)資料

| 型號: | IDT88P8342BHI |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 88/98頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 標準包裝: | 24 |

| 系列: | * |

| 其它名稱: | 88P8342BHI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁當前第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

89

IDT88P8342 SPI EXCHANGE 2 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

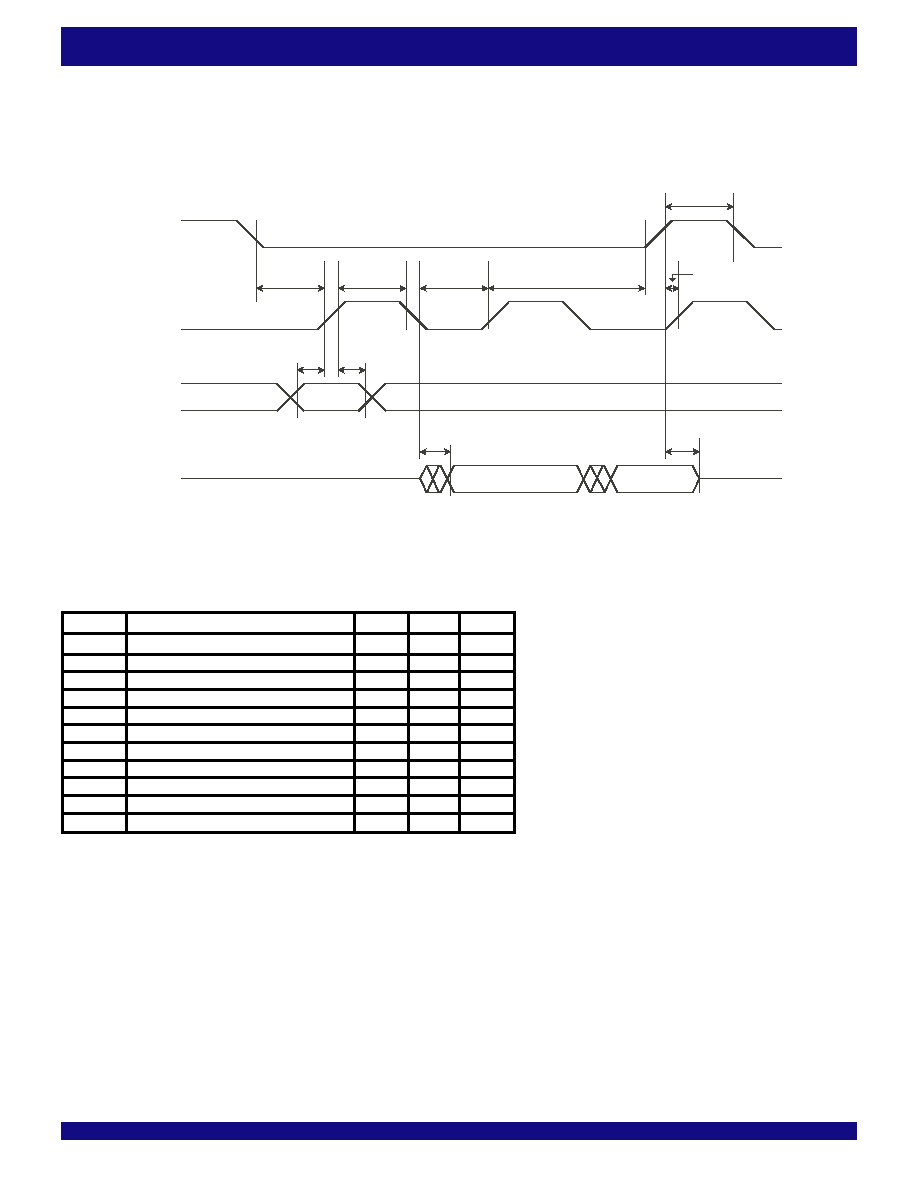

6370 drw11

SCLK

tCSH

High Impedance

Valid Input

tCLD

tCSD

tCLL

tCLH

tCSS

tDIS

tDIH

tPD

Valid Output

tDF

High Impedance

SDI

SDO

CSB

11.6.6.2 Serial microprocessor interface (serial

peripheral interface mode)

Timing Characteristics

The maximum SPI Data transfer clock frequency is 2 MHz. The detail

informationofthetimingcharacteristicsisshowninbelowandtimingdiagramis

showninFigure41,Microprocessorserialperipheralinterfacetimingdiagram.

Symbol

Description

Min.

Max.

Unit

fOP

SCLK Frequency

2.0

MHz

fCSH

Minimum CSB High Time

100

ns

tCSS

CSB Setup Time

50

ns

tCSD

CSB Hold Time

100

ns

tCLD

SCLK Clock Disable Time

50

ns

tCLH

SCLK Clock High Time

205

ns

tCLL

SCLK Clock Low Time

205

ns

tDIS

SDI Data Setup Time

50

ns

tDIH

SDI Data Hold Time

150

ns

tPD

SDO Output Delay

150

ns

tDF

SDO Output Disable Time

50

ns

Figure 41. Microprocessor serial peripheral interface timing diagram

TABLE 142 – MICROPROCESSOR SERIAL PERIPHERAL INTERFACE TIMING

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT88P8344BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT89H24NT24G2ZBHLG | IC PCI SW 24LANE 24PORT 324BGA |

| IDT89HPES16NT2ZBBCG | IC PCI SW 16LANE 2PORT 484-CABGA |

| IDT89HPES24NT3ZBBXG | IC PCI SW 24LANE 3PORT 420-SBGA |

| IDT89HPES32T8ZHBXG | IC PCI SW 32LANE 8PORT 500-SBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT88P8344 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBC8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。