- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1924 > IDT88P8342BHI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF資料下載

參數(shù)資料

| 型號: | IDT88P8342BHI |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 27/98頁 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | * |

| 其它名稱: | 88P8342BHI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

33

IDT88P8342 SPI EXCHANGE 2 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

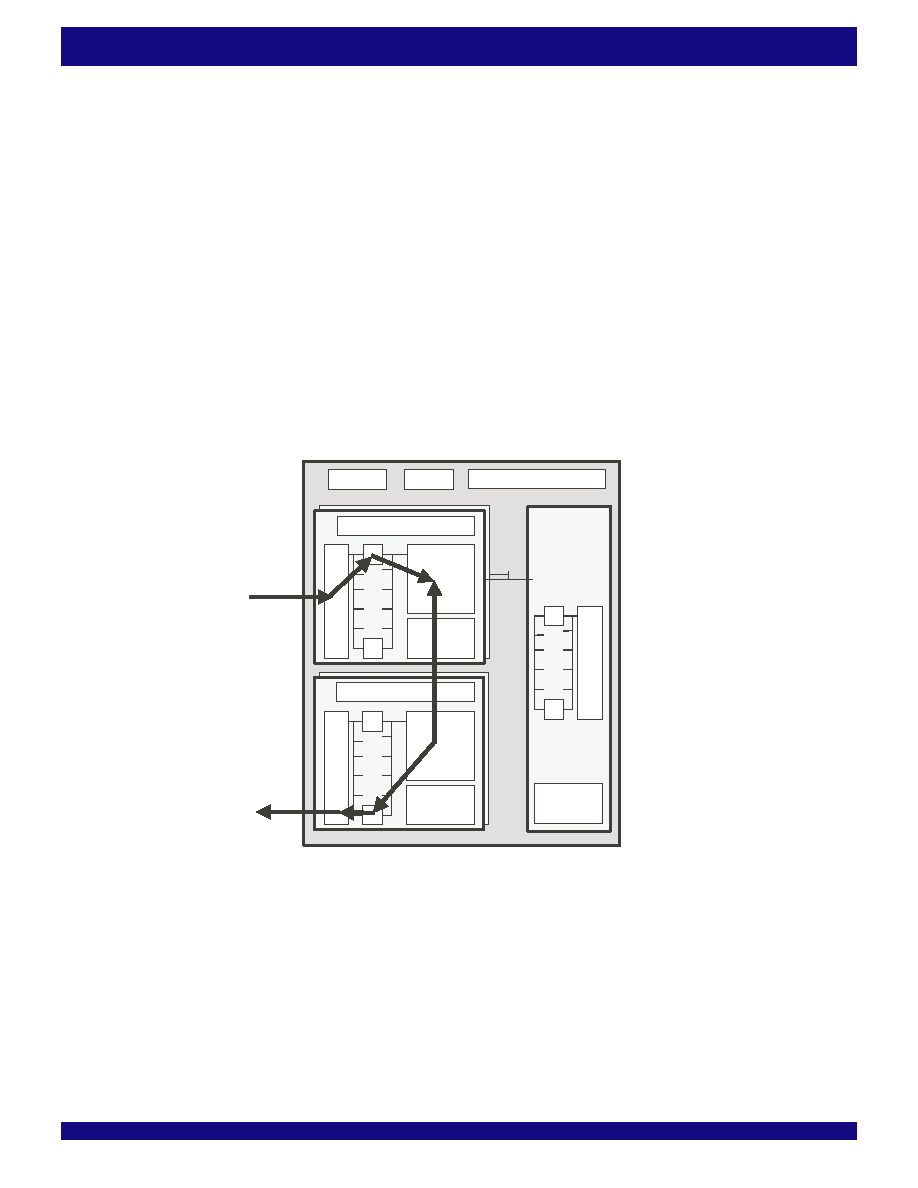

4.3 SPI-3 ingress to SPI-3 egress datapath

TheSPI-3redirectbuffercanstoreSPI-3packetfragments.Thestatusofthe

packetfragmentbuffersisforwardedtotheassociatedpacketfragmentproces-

sor. The purpose of the SPI-3 redirect is to enable per-LP flows between

physical interfaces SPI-3 A and SPI-3 B. Other flows between SPI-3 ports are

not allowed; i.e., between A and A, and between B and B.

The following is a description of the path taken by a fragment of data through

the device.

A SPI-3 to SPI-3 path is between an LP on one SPI-3 to the paired SPI-3.

Data enters on the SPI-3 interface in fragments. Fragments are of equal length

except the last fragment of a packet which may be shorter. The LP address is

in-band with the data. The packet fragment enters an ingress buffer. SPI-3 LP

address, error information, SOP, and EOP information is are stored with the

fragment. The LP address is mapped to a LID. The fragment is stored in buffer

segment pool per-LID-allocated memory space.

The Table 80, SPI-3 egress port descriptor table (64 entries) is consulted,

and the PFP decides to send a LID to the associated SPI-3 egress port. The

SPI-3 packet fragment processor chooses the next LP. The choice of LP is

dependent on status of the LP and availability of a complete fragment. Data is

moved to an egress buffer along with the SPI-3 LP address, error information,

SOP,andEOPinformation.DataistransmittedinpacketfragmentsoveraSPI-

3interface.

The paths to and from the microprocessor interface can be used to perform

mappings from a SPI-3 LP to a SPI-3 LP where not provided, and from a SPI-

4 to a SPI-4 LP. However these paths are limited by the bandwidth of the

microprocessorinterface.

The diagram below shows the datapath through the device from a SPI-3

interfacetoitspairedSPI-3interface.FortheSPI-3redirect,theLIDconnecting

associated port pairs must be the same in both directions.

Figure 21. SPI-3 ingress to SPI-3 egress datapath

…

SPI-3 /

LID map

…

SPI-3

8 bit / 32 bit

Min: 19.44MHz

Max: 133MHz

SPI-3

8 bit / 32 bit

Min: 19.44MHz

Max: 133MHz

SPI-4.2

Min: 80 MHz

Max: 400 MHz

JTAG

uproc

Chip Counters Memory

LID Counters Memory

Interface

Bloc

k

SPI-4 /

LID map

SPI-3 /

LID map

LID Counters Memory

Main

Memory

A

Main

Memory

B

6370 drw14

Interface

Bloc

k

Interface

Bloc

k

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT88P8344BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT89H24NT24G2ZBHLG | IC PCI SW 24LANE 24PORT 324BGA |

| IDT89HPES16NT2ZBBCG | IC PCI SW 16LANE 2PORT 484-CABGA |

| IDT89HPES24NT3ZBBXG | IC PCI SW 24LANE 3PORT 420-SBGA |

| IDT89HPES32T8ZHBXG | IC PCI SW 32LANE 8PORT 500-SBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT88P8344 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBC8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。