- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379205 > IBM25CPC710AB3A100 (IBM Microeletronics) IBM Dual Bridge and Memory Controller(IBM雙橋和存儲(chǔ)器控制器(連接帶同步動(dòng)態(tài)RAM存儲(chǔ)器的Power PC 60x總線和兩個(gè)PCI端口)) PDF資料下載

參數(shù)資料

| 型號(hào): | IBM25CPC710AB3A100 |

| 廠商: | IBM Microeletronics |

| 英文描述: | IBM Dual Bridge and Memory Controller(IBM雙橋和存儲(chǔ)器控制器(連接帶同步動(dòng)態(tài)RAM存儲(chǔ)器的Power PC 60x總線和兩個(gè)PCI端口)) |

| 中文描述: | IBM的雙橋和內(nèi)存控制器(IBM的雙橋和存儲(chǔ)器控制器(連接帶同步動(dòng)態(tài)RAM的存儲(chǔ)器的Power PC處理器60倍的PCI總線和兩個(gè)端口)) |

| 文件頁數(shù): | 29/224頁 |

| 文件大小: | 3278K |

| 代理商: | IBM25CPC710AB3A100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁

IBM25CPC710AB3A100

IBM Dual Bridge and Memory Controller

dbamc01_ch2.fm.01

July 13, 2000

Page 17 of 208

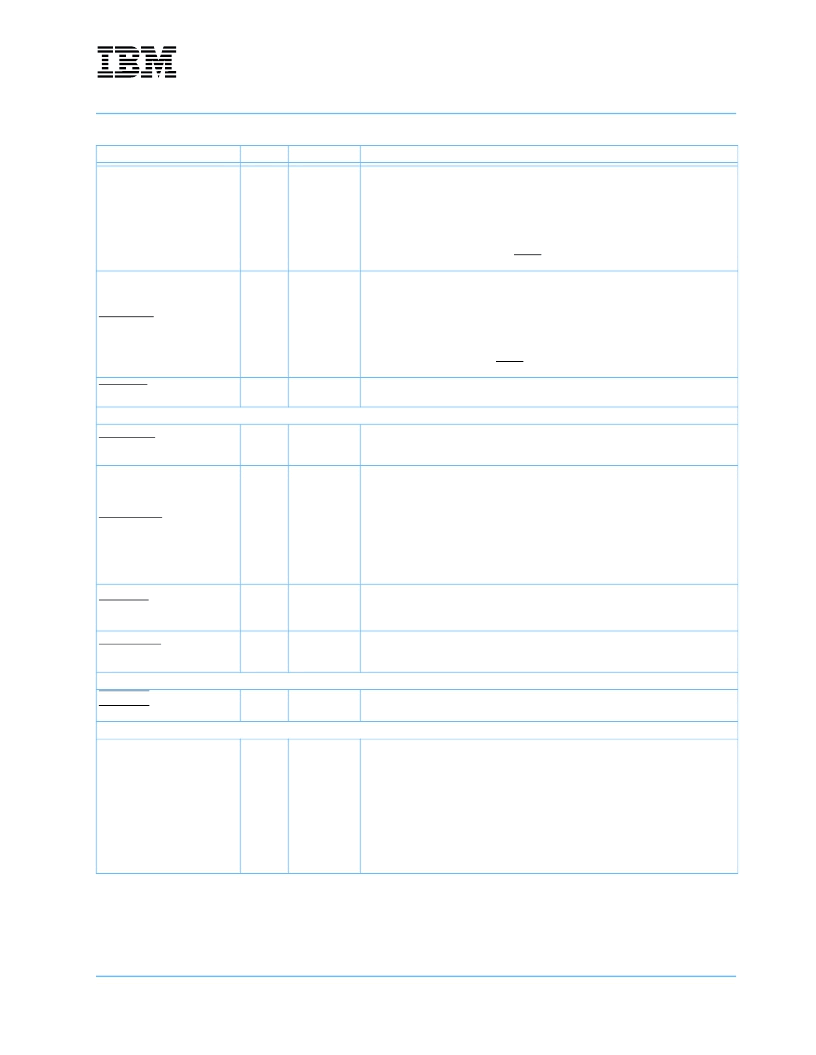

SYS_TSIZ[0:2]

I/O

Pull-up

Transfer Size.

Output signals and the TBST signal

: Indicate the data transfer size of

the operation. Device sets these signals to a value stored in the ATAS

register for the operations it initiates.

Input signals and the TBST signal

: For normal memory accesses,

indicate the data transfer size of the operation. For XferData instruc-

tions (eciwx and ecowx), they indicate the 4-bit Resource ID (RID) of

the XferData operation (TBST || TSIZ0-TSIZ2).

Transfer Burst.

Output signal and the TSIZ signals:

Indicate the data transfer size of

the operation. Device sets this signal according to the bit in the ATAS

register for operations it initiates.

Input signal:

For normal memory accesses, indicates a burst transfer

is in progress. For XferData instructions (eciwx and ecowx), the input

signal and the TSIZ signals indicate the 4-bit Resource ID (RID) of the

XferData operation (TBST || TSIZ0-TSIZ2).

Global.

Always asserted by device for transactions, it initiates to indicate all

devices on the 60x bus must snoop the transaction.

SYS_TBST

I/O

Pull-up

SYS_GBL

O

Tri-state

pull-up

Address Transfer Termination Signals

SYS_AACK

O

Address Acknowledge.

Indicates the address tenure is complete and the

ARTRY sampling window ends on the following bus cycle. Address bus and

transfer attribute signals must go to tri-state on the next bus cycle.

Address Retry.

Output

indicates device detects a condition that requires an address

tenure to be retried.

Input

: When asserted in response to a device cache operation, device

assumes the cache line is modified and/or present in a CPU or L2

cache. Device then retries the operation on the PCI bus and address

tenure is not rerun until the device on the PCI bus reruns its transfer.

The pre-charge logic is always signaled to initiate the pre-charge

sequence.

Shared.

Output

: Not applicable; Device only pre-charges the signal.

Input:

Instructs the pre-charge logic to initiate a pre-charge sequence.

L2 Hit:

Indicates an external slave has been addressed by the current master.

The device arbiter uses this signal to confirm positive selection of an address

tenure on the 60x bus. Not available with SDRAM memory.

SYS_ARTRY

I/O

SYS_SHD

I/O

Pull-up

SYS_L2_HIT

I

Pull-up

Data Bus Arbitration Signals

SYS_DBG0

SYS_DBG1

Data Transfer Signals

O

Data Bus Grant.

Indicates the device associated with this signal may, with the

proper qualification, assume mastership of the data bus.

SYS_DATA[0:63]

I/O

Pull-up

Data Bus.

Byte 0: D[0:7] - DH[0:7]

Byte 1: D[8:15] - DH[8:15]

Byte 2: D[16:23] - DH[16:23]

Byte 3: D[24:31] - DH[24:31]

Byte 4: D[32:39] - DL[0:7]

Byte 5: D[40:47] - DL[8:15]

Byte 6: D[48:55] - DL[16:23]

Byte 7: D[56:63] - DL[24:31]

Table 3: 60x Bus Interface Signals

(Page 2 of 3)

Signal Name

I/O

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM3206K0424 | IBM Processor for Network Resources(異步轉(zhuǎn)換模式(ATM)32位微處理器(用于網(wǎng)絡(luò)資源管理)) |

| IBM3209K3114 | IBM Packet Routing Switch Serial Interface Converter(IBM封裝路線選擇開關(guān)串行接口轉(zhuǎn)換器) |

| IBM32NPCXX1EPABBE66 | IBM Processor for Network Resources(異步轉(zhuǎn)換模式(ATM)32位微處理器(用于網(wǎng)絡(luò)資源管理)) |

| IBM39MPEGCS24DPFA16C | High Performance Audio/Video Decoder(高性能音頻/視頻譯碼器) |

| IBM39MPEGCS24PFA16C | High Performance Audio/Video Decoder(高性能音頻/視頻譯碼器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM25CPC710BB3B100 | 制造商:IBM 功能描述: |

| IBM25CPC710CF3B133 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PERIPHERAL (MULTIFUNCTION) CONTROLLER |

| IBM25EB750CLWINHCK00 | 制造商:IBM Microelectronics 功能描述:750CL REF DES KIT - HW & SW - Boxed Product (Development Kits) 制造商:IBM 功能描述:IBM IBM25EB750CLWINHCK00 Development Kits |

| IBM25EB750GXWINHIC00 | 制造商:IBM 功能描述:750GX REF DESIGN KIT, HDW & SOFTWARE - Boxed Product (Development Kits) |

| IBM25EMPPC740DBUB2330 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。