- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370745 > HYB18L256160BF-7.5 (INFINEON TECHNOLOGIES AG) RT ANG PCB CONT .40/1.295 BULK PDF資料下載

參數(shù)資料

| 型號: | HYB18L256160BF-7.5 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | RT ANG PCB CONT .40/1.295 BULK |

| 中文描述: | BJAWBMSpecialty DRAM的移動RAM |

| 文件頁數(shù): | 26/49頁 |

| 文件大小: | 1327K |

| 代理商: | HYB18L256160BF-7.5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

HY[B/E]18L256160B[C/F]-7.5

256-Mbit Mobile-RAM

Functional Description

Data Sheet

26

V1.4, 2004-04-30

2.4.5.3

DQM may be used to suppress read data and place the output buffers into High-Z state. The generic timing

parameters as listed in

Table 10

also apply to this DQM operation. The read burst in progress is not affected and

will continue as programmed.

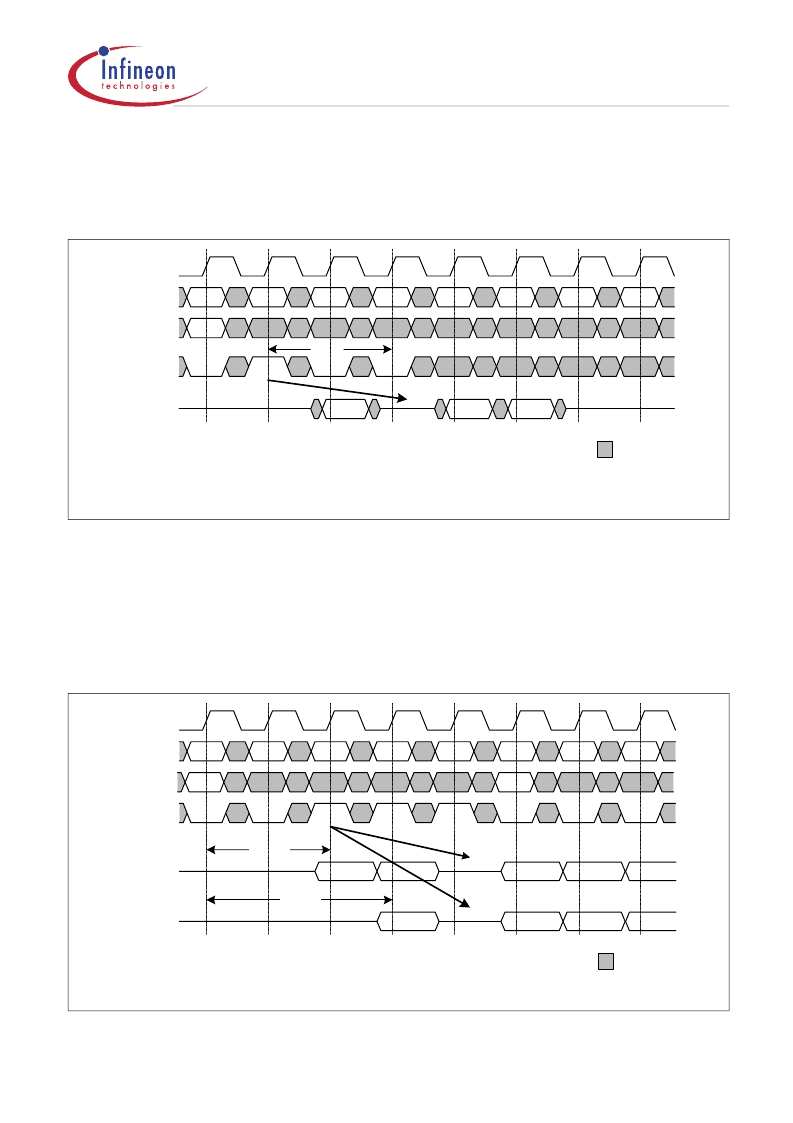

READ - DQM Operation

Figure 20

READ Burst - DQM Operation

2.4.5.4

A READ burst may be followed by or truncated with a WRITE command. The WRITE command can be performed

to the same or a different (active) bank. Care must be taken to avoid bus contention on the DQs; therefore it is

recommended that the DQs are held in High-Z state for a minimum of 1 clock cycle. This can be achieved by either

delaying the WRITE command, or suppressing the data-out from the READ by pulling DQM HIGH two clock cycles

prior to the WRITE command, as shown in

Figure 21

. With the registration of the WRITE command, DQM acts as

a write mask: when asserted HIGH, input data will be masked and no write will be performed.

READ to WRITE

Figure 21

READ to WRITE Timing

Ba A, Col n = bank A, column n

DO n = Data Out from column n

CL = 2 in the case shown.

DQM read latency t

DQZ

is 2 clock cycles

= Don't Care

CLK

Command

NOP

READ

NOP

NOP

NOP

NOP

NOP

NOP

DQM

t

DQZ

Address

Ba A,

Col n

DQ

DO n+2

DO n

DO n+3

Ba A, Col n (b) = bank A, column n (b)

DO n = Data Out from column n; DI b = Data In to column b;

DQM is asserted HIGH to set DQs to High-Z state for 1 clock cycle prior to the WRITE command.

= Don't Care

CLK

CL=2

CL=3

Command

NOP

READ

NOP

NOP

NOP

NOP

NOP

WRITE

Address

Ba A,

Col b

Ba A,

Col n

DQM

DQ

DO n

DI b

DI b+1

DO n+1

High-Z

DI b+2

DQ

DI b

DI b+1

DO n

High-Z

DI b+2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18RL25632AC-4 | MEMORY SPECTRUM |

| HYC3N2560NO50AA1AA | CAP 560PF 100V 10% X7R AXIAL TR-14 |

| HYB18S128160TE-3 | 122 x 32 pixel format, LED Backlight available |

| HYB25S128160TE-3 | 122 x 32 pixel format, LED Backlight available |

| HYB18D128160TE-3 | 122 x 32 pixel format, LED Backlight available |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18L256160BFL-7.5 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:DRAMs for Mobile Applications 256-Mbit Mobile-RAM |

| HYB18L256160BFX-7.5 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:DRAMs for Mobile Applications 256-Mbit Mobile-RAM |

| HYB18L2561660BF-7.5 | 制造商:QIMONDA 功能描述: |

| HYB18L256169BF | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:256-Mbit Mobile-RAM |

| HYB18L256169BF-7.5 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:256-Mbit Mobile-RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。