- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370395 > GT28F320D18B110 x16 Flash EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | GT28F320D18B110 |

| 英文描述: | x16 Flash EEPROM |

| 中文描述: | x16閃存EEPROM |

| 文件頁(yè)數(shù): | 19/83頁(yè) |

| 文件大小: | 836K |

| 代理商: | GT28F320D18B110 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)

28F320D18

Product Preview

15

NOTE:

1. Commands other than those shown above are reserved by Intel for future device implementations and

should not be used.

2.

First cycle command addresses should be the same as the operation’s target address. Examples: the first-

cycle address for the Read Device Identification Codes command should be the same as the Identification

Code address (IA); the first cycle address for the Program command should be the same as the word

address (WA) to be programmed; the first cycle address for the Erase/Program Suspend command should

be the same as the address within the block to be suspended; etc.

CA = Identification code address.

BA = Address within the block.

LPA = Lock Protection Address is obtained from the CFI (via the Read Query command). 1.8 V Dual-Plane

Flash memory’s LPA is at 0080h.

PA = User programmable 4-word protection address in the device identification plane.

PnA = Address within the partition.

QA = Query code address.

WA = Word address of memory location to be written.

3. SRD = Data read from the status register.

WD = Data to be written at location WA is latched on the rising edge of WE# or CE# (whichever goes high

first).

CD = Identifier code data.

PD =User programmable 4-word protection data.

QD = Query code data.

RCD = Read Configuration register code data presented on device addresses A

. Upper address bits can

select either partition

.

See

Table 8

for read configuration register bits descriptions.

4. Following the Read Device Identification Codes or Read Query commands, read operations output

manufacturer and device configuration or CFI query information and the read configuration register.

5. Read Device Identification and Read Query addresses must be within the bottom partition.

6. Following a block erase, program, and suspend operation, read operations access the status register.

7. The WSM recognizes either 40H or 10H program setup commands.

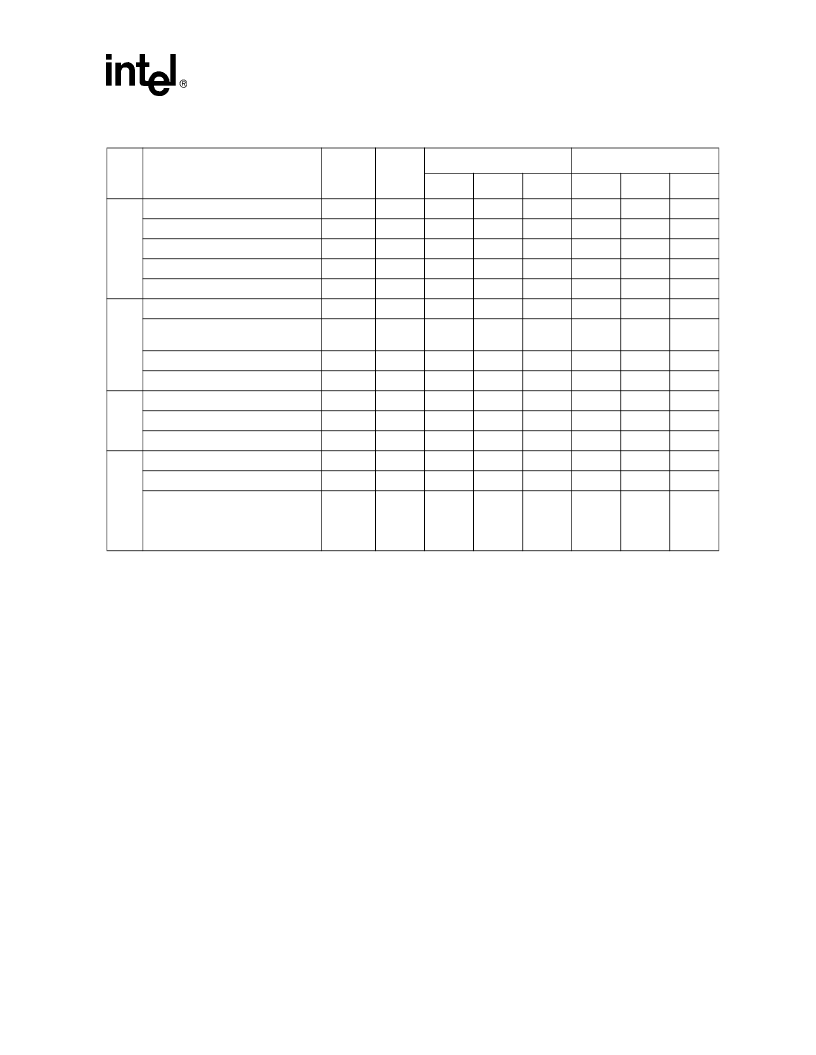

Table 5. Command Definitions

(1)

Bus

Cycles

Notes

First Bus Cycle

Second Bus Cycle

Command

Oper

Addr

(2)

Data

(3)

Oper

Addr

(2

Data

(3)

R

Read Array/Reset

1

Write

PnA

FFH

Read Device Identification Codes

≥

2

4,5

Write

CA

90H

Read

CA

CD

Read Query

≥

2

4,5

Write

QA

98H

Read

QA

QD

Read Status Register

2

Write

BA

70H

Read

BA

SRD

Clear Status Register

1

Write

BA

50H

P

E

Block Erase

2

7

Write

BA

20H

Write

BA

D0H

Program

2

6, 7

Write

WA

40H/

10H

Write

WA

WD

Program/Erase Suspend

1

6

Write

BA

B0H

Program/Erase Resume

1

6

Write

BA

D0H

L

Lock Block

2

Write

BA

60H

Write

BA

01H

Unlock Block

2

Write

BA

60H

Write

BA

D0H

Lock-down Block

2

Write

BA

60H

Write

BA

2FH

C

Protection Program

2

Write

PA

C0H

Write

PA

PD

Lock Protection Program

2

Write

LPA

C0H

Write

LPA

FFFDH

Set Read Configuration Register

2

2, 5

Write

RCD

60H

Write

RCD

03H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GT28F320D18B120 | x16 Flash EEPROM |

| GT3-20DP-2.5DSA | Antenna, Sensor, and Communications Trunk Line Connections |

| GT3TK-36DP-DSA | Antenna, Sensor, and Communications Trunk Line Connections |

| GT3TK-48TP-DS | Antenna, Sensor, and Communications Trunk Line Connections |

| GT3-16DP-2.5DSA | Antenna, Sensor, and Communications Trunk Line Connections |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GT28F320D18B120 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x16 Flash EEPROM |

| GT28F320S3-100 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:WORD-WIDE FlashFile⑩ MEMORY FAMILY |

| GT28F320S3-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:WORD-WIDE FlashFile MEMORY FAMILY |

| GT28F320W18BC60 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel? Wireless Flash Memory |

| GT28F320W18BC80 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel? Wireless Flash Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。