- 您現(xiàn)在的位置:買賣IC網 > PDF目錄1916 > DS34S132GN+ (Maxim Integrated Products)IC TDM OVER PACKET 676-BGA PDF資料下載

參數(shù)資料

| 型號: | DS34S132GN+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 180/194頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC TDM OVER PACKET 676-BGA |

| 產品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 40 |

| 功能: | TDM-over-Packet(TDMoP) |

| 接口: | TDMoP |

| 電路數(shù): | 1 |

| 電源電壓: | 1.8V, 3.3V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 676-BGA |

| 供應商設備封裝: | 676-PBGA(27x27) |

| 包裝: | 管件 |

| 其它名稱: | 90-34S13+2N0 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁當前第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁

DS34S132 DATA SHEET

19-4750; Rev 1; 07/11

86 of 194

G. Field

Name

Addr (A:)

Bit [x:y] Type

Description

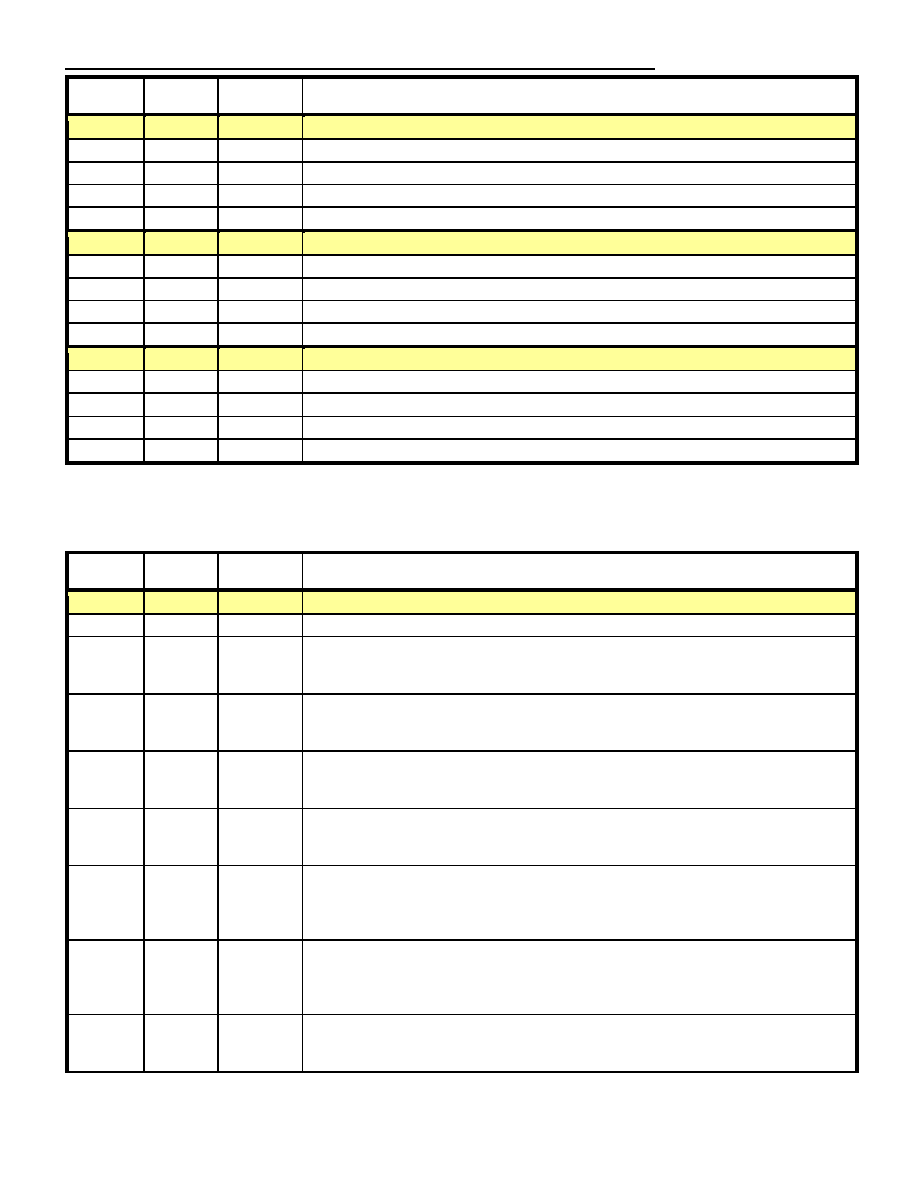

ECCR2.

A:0014h

Ethernet Conditioning Configuration Register 2. Default: 0x00.00.00.00

ECOE

[31:24] rwc-_-_

Ethernet Conditioning Octet E. TXP Ethernet Conditioning Octet E

ECOF

[23:16] rwc-_-_

Ethernet Conditioning Octet F. TXP Ethernet Conditioning Octet F

ECOG

[15:8] rwc-_-_

Ethernet Conditioning Octet G. TXP Ethernet Conditioning Octet G

ECOH

[7:0] rwc-_-_

Ethernet Conditioning Octet H. TXP Ethernet Conditioning Octet H

TCCR1.

A:0018h

TDM Conditioning Configuration Register 1. Default: 0x00.00.00.00

TCOA

[31:24] rwc-_-_

TDM Conditioning Octet A. RXP TDM Conditioning Octet A.

TCOB

[23:16] rwc-_-_

TDM Conditioning Octet B. RXP TDM Conditioning Octet B

TCOC

[15:8] rwc-_-_

TDM Conditioning Octet C. RXP TDM Conditioning Octet C

TCOD

[7:0] rwc-_-_

TDM Conditioning Octet D. RXP TDM Conditioning Octet D

TCCR2.

A:001Ch

TDM Conditioning Configuration Register 2. Default: 0x00.00.00.00

ETCOE

[31:24] rwc-_-_

TDM Conditioning Octet E. RXP TDM Conditioning Octet E

TCOF

[23:16] rwc-_-_

TDM Conditioning Octet F. RXP TDM Conditioning Octet F

TCOG

[15:8] rwc-_-_

TDM Conditioning Octet G. RXP TDM Conditioning Octet G

TCOH

[7:0] rwc-_-_

TDM Conditioning Octet H. RXP TDM Conditioning Octet H

10.3.1.2 Global Status Registers (G.)

Table 10-4. Global Status Registers (G.)

G. Field

Name

Addr (A:)

Bit [x:y] Type

Description

GSR1.

A:0030h

Global Status Register 1. Default: 0x00.00.00.00

RSVD

[31:18]

Reserved.

EBS

[17] ros-_-i1

Encap (Ethernet) BERT Status = “1” indicates one or more Packet BERT Status

Latch bits = “1” (EB.BSRL) and are enabled (EB.BSIE). The combination of EBS =

1 and G.GSRIE1.EBIE = 1 forces an interrupt on INT_N.

DBS

[16] ros-_-i1

Decap (TDM Port) BERT Status = “1” indicates one or more TDM BERT Status

Latch bits = “1” (DB.BSRL) and are enabled (DB.BSIE). The combination of DBS

= 1 and G.GSRIE1.DBIE = 1 forces an interrupt on INT_N.

PTCS

[15] ros-_-i1

Port Transmit CAS Status = “1” indicates one or more Transmit (RXP) CAS

Status Latch bits = “1” (G.GSR2) and are enabled (G.GSRIE2). The combination

of PTCS = 1 and G.GSRIE1.PTCIE = 1 forces an interrupt on INT_N.

PRCS

[14] ros-_-i1

Port Receive CAS Status = “1” indicates one or more Receive (TXP) CAS Status

Latch bits = “1” (G.GSR3) and are enabled (G.GSRIE3). The combination of

PRCS = 1 and G.GSRIE1.PRCIE = 1 forces an interrupt on INT_N.

MIRS

[13] ros-_-i1

MAC Interrupt Register Status = “1” indicates one or more M.IRQ_STATUS

Status Latch bits = “1” and are enabled (M.IRQ_ENABLE and M.IRQ_DISABLE).

The combination of MIRS = 1 and G.GSRIE1.MIRIE = 1 forces an interrupt on

INT_N.

CRHS

[12:8] ros-_-i1

Clock Recovery Hardware Status = “1” indicates one or more Clock Recovery

Engine Status Latch bits = “1” (the Clock Recovery Status is defined by the DSP

Firmware load). The combination of any CRHS[x] = 1 (x = 8 to 12) and

G.GSRIE1.CRHIE[x] = 1 forces an interrupt on INT_N.

BS

[7] ros-_-i1

Bundle Status = “1” indicates one or more Group Bundle Status bits are “1”

(G.GSR5). The combination of BS = 1 and G.GSRIE1.BIE = 1 forces an interrupt

on INT_N.

相關PDF資料 |

PDF描述 |

|---|---|

| DS34T102GN+ | IC TDM OVER PACKET 484TEBGA |

| DS3501U+H | IC POT NV 128POS HV 10-USOP |

| DS3502U+ | IC POT DGTL NV 128TAP 10-MSOP |

| DS3503U+ | IC POT DGTL NV 128TAP 10-MSOP |

| DS3897MX | IC TXRX BTL TRAPEZIODAL 20-SOIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DS34S132GN+ | 功能描述:通信集成電路 - 若干 32Port TDM-Over-Pack Transport Device RoHS:否 制造商:Maxim Integrated 類型:Transport Devices 封裝 / 箱體:TECSBGA-256 數(shù)據(jù)速率:100 Mbps 電源電壓-最大:1.89 V, 3.465 V 電源電壓-最小:1.71 V, 3.135 V 電源電流:50 mA, 225 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Tube |

| DS34S132GNA2+ | 功能描述:通信集成電路 - 若干 32Port TDM-Over-Pack Transport Device RoHS:否 制造商:Maxim Integrated 類型:Transport Devices 封裝 / 箱體:TECSBGA-256 數(shù)據(jù)速率:100 Mbps 電源電壓-最大:1.89 V, 3.465 V 電源電壓-最小:1.71 V, 3.135 V 電源電流:50 mA, 225 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Tube |

| DS34T101 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Single/Dual/Quad/Octal TDM-over-Packet Chip |

| DS34T101_08 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Single/Dual/Quad/Octal TDM-over-Packet Chip |

| DS34T101_09 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Single/Dual/Quad/Octal TDM-over-Packet Chip |

發(fā)布緊急采購,3分鐘左右您將得到回復。