- 您現在的位置:買賣IC網 > PDF目錄1915 > DS26303LN-75+A3 (Maxim Integrated Products)IC LIU E1/T1/J1 3.3V 144-ELQFP PDF資料下載

參數資料

| 型號: | DS26303LN-75+A3 |

| 廠商: | Maxim Integrated Products |

| 文件頁數: | 10/101頁 |

| 文件大小: | 0K |

| 描述: | IC LIU E1/T1/J1 3.3V 144-ELQFP |

| 產品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 1 |

| 類型: | 線路接口裝置(LIU) |

| 驅動器/接收器數: | 8/8 |

| 規(guī)程: | T1/E1/J1 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LQFP 裸露焊盤 |

| 供應商設備封裝: | 144-LQFP 裸露焊盤 |

| 包裝: | 托盤 |

| 其它名稱: | 90-26303+7N3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁

DS26303: 3.3V, T1/E1/J1, Short-Haul, Octal Line Interface Unit

16 of 101

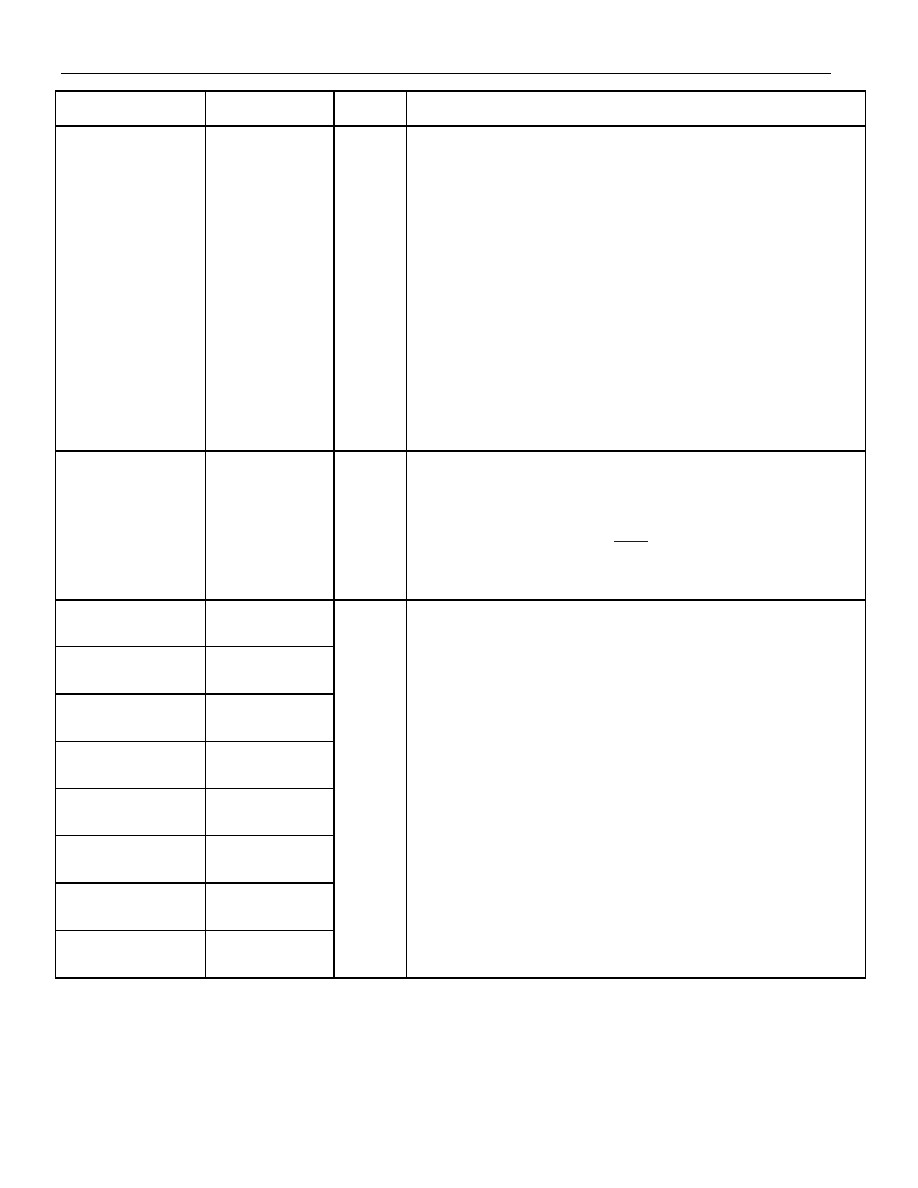

NAME

PIN

TYPE

FUNCTION

SDO/RDY/ACKB/

RIMPOFF

83

I/O

Serial Data Out/Ready Output/Acknowledge Bar/Receive

Impedance Off

SDO:

In serial host mode, the SDO data is output on this pin. If a

serial write is in progress this pin is in high impedance. During a

read SDO is high impedance when SDI is in command/

address mode. If CLKE is low, SDO is output on the rising edge of

SCLK, if CLKE is high, SDO is output on the falling edge. Data is

output LSB first.

RDY:

A low on this pin reports to the host that the cycle is not

complete and wait states must be inserted. A high means the

cycle is complete.

ACKB:

In Motorola parallel mode, a low on this pin indicates that

the read data is available for the host or that the written data cycle

is complete.

RIMPOFF:

In hardware mode when this input pin is high, all the

RTIP and RING pins have internal impedance switched off.

INTB

82

O,

open

drain

Active-Low Interrupt Bar.

This interrupt signal is driven low when

an event is detected on any of the enabled interrupt sources in any

of the register banks. When there are no active and enabled

interrupt sources, the pin can be programmed to either drive high

or not drive high (see Section 4.1.4). The reset default is to not

drive high when there are no active enabled interrupt sources. All

interrupt sources are disabled after a software reset and they must

be programmed to be enabled.

D7/AD7/LP8

28

D6/AD6/LP7

27

D5/AD5/LP6

26

D4/AD4/LP5

25

D3/AD3/LP4

24

D2/AD2/LP3

23

D1/AD1/LP2

22

D0/AD0/LP1

21

I/O (In

HW

mode,

pulled

to

VDDIO/2)

Data Bus 7–0/Address/Data Bus 7–0/Loopback Select 8–1

D[7:0]:

In nonmultiplexed host mode, these pins are the

bidirectional data bus.

AD[7:0]:

In multiplexed host mode, these pins are the bidirectional

address/data bus. Note that AD7 and AD6 do not carry address

information, and in serial host mode AD6–AD0 should be

grounded.

In serial host mode, this pin should be tied low.

LP[8:1]

In hardware mode, these pins set the loopback modes for

the corresponding LIU as follows:

Low → Remote Loopback

VDDIO/2 → No Loopback

High → Analog Loopback

Note: When left unconnected in hardware mode, do not route

signals with fast transitions near LP1–LP8. This practice minimizes

capacitive coupling.

相關PDF資料 |

PDF描述 |

|---|---|

| DS26324GNA2+ | IC INTERFACE LINE 16CH 256-CSBGA |

| DS26334GN+ | IC INTERFACE LINE 16CH 256-CSBGA |

| DS26401N+ | IC OCTAL FRAMER T1/E1/J1 256-BGA |

| DS26504LNB2+ | IC T1/E1/J1 64KCC ELEMENT 64LQFP |

| DS26514G+ | IC TXRX T1/E1/J1 4PORT 256-CSBGA |

相關代理商/技術參數 |

參數描述 |

|---|---|

| DS26303LN-XXX | 制造商:DALLAS 制造商全稱:Dallas Semiconductor 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26303LN-XXX+ | 制造商:DALLAS 制造商全稱:Dallas Semiconductor 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26303L-XXX | 制造商:DALLAS 制造商全稱:Dallas Semiconductor 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26303L-XXX+ | 制造商:DALLAS 制造商全稱:Dallas Semiconductor 功能描述:3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit |

| DS26-32.768-STD-020 | 制造商:Micro Crystal Switzerland 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。