- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄256256 > BX80528KL150GD (INTEL CORP) 32-BIT, 1500 MHz, MICROPROCESSOR, CPGA603 PDF資料下載

參數(shù)資料

| 型號(hào): | BX80528KL150GD |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 1500 MHz, MICROPROCESSOR, CPGA603 |

| 封裝: | PGA-603 |

| 文件頁(yè)數(shù): | 97/116頁(yè) |

| 文件大小: | 2277K |

| 代理商: | BX80528KL150GD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)當(dāng)前第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)

Intel XeonTM Processor MP

Datasheet

81

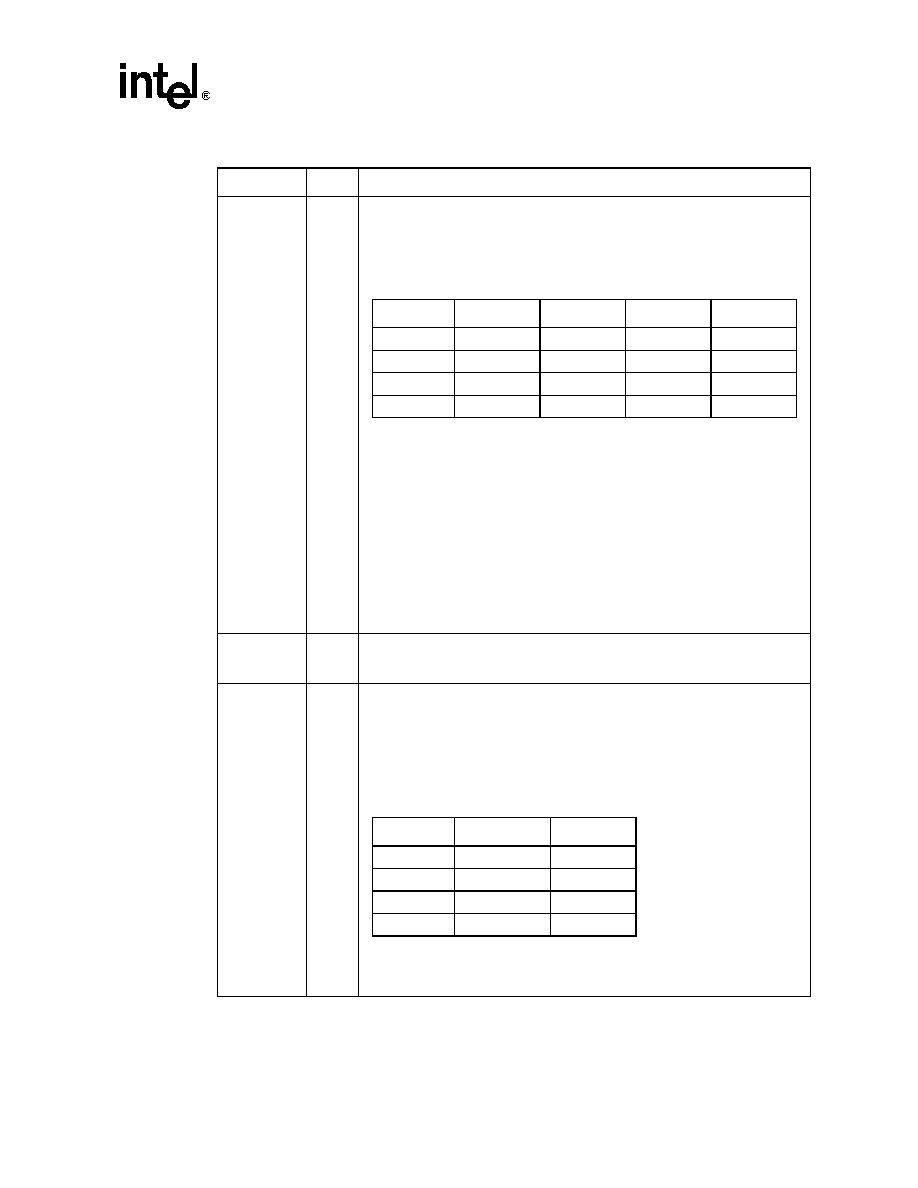

BR0#

BR[1:3]#

I/O

I

BR[3:0]# (Bus Request) drive the BREQ[3:0]# signals in the system. The BREQ[3:0]#

signals are interconnected in a rotating manner to individual processor pins. The tables

below give the rotating interconnect between the processor and bus signals for 2-way and 4-

way systems.

During power-on configuration, the central agent must assert the BREQ0# bus signal. All

symmetric agents sample their BR[3:0]# pins on the active-to-inactive transition of

RESET#. The pin which the agent samples asserted determines it’s agent ID.

These signals do not have on-die termination and must be terminated at the end agent.

COMP[1:0]

I

COMP[1:0] must be terminated to VSS on the system board using precision resistors. These

inputs configure the AGTL+ drivers of the processor. Refer to the appropriate platform

design guidelines and Table 12 for implementation details.

D[63:0]#

I/O

D[63:0]# (Data) are the data signals. These signals provide a 64-bit data path between the

processor system bus agents, and must connect the appropriate pins on all such agents. The

data driver asserts DRDY# to indicate a valid data transfer.

D[63:0]# are quad-pumped signals, and will thus be driven four times in a common clock

period. D[63:0]# are latched off the falling edge of both DSTBP[3:0]# and DSTBN[3:0]#.

Each groupof16datasignals correspondtoapair of oneDSTBP#and one DSTBN#. The

following table shows the grouping of data signals to strobes and DBI#.

Furthermore, the DBI# pins determine the polarity of the data signals. Each group of 16 data

signals corresponds to one DBI# signal. When the DBI# signal is active, the corresponding

data group is inverted and therefore sampled active high.

Table 33. Signal Definitions (Page 3 of 8)

Name

Type

Description

BR[3:0]# Signals Rotating Interconnect, 4-way system (Intel Xeon processor MP

processors only)

Bus Signal

Agent 0 Pins

Agent 1 Pins

Agent 2 pins

Agent 3 pins

BREQ0#

BR0#

BR3#

BR2#

BR1#

BREQ1#

BR1#

BR0#

BR3#

BR2#

BREQ2#

BR2#

BR1#

BR0#

BR3#

BREQ3#

BR3#

BR2#

BR1#

BR0#

Data Group

DSTBN/DSTBP

DBI#

D[15:0]#

0

D[31:16]#

1

D[47:32]#

2

D[63:48]#

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61740B3-200L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61740B4-200L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61740B4-400L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61840B3-300 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61840B3-302W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BX80530C1000256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| BX80530C1133256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| BX80530C1200256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| BX80530C1400512 | 制造商:Intel 功能描述:MPU PENTIUM III PROCESSOR 64-BIT 0.13UM 1.4GHZ 370-PIN FCPG - Boxed Product (Development Kits) |

| BX80530F1100256 | 制造商:Intel 功能描述:CELERON PROCESSOR - Boxed Product (Development Kits) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。