- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376460 > XRT16C854 (Exar Corporation) 2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO PDF資料下載

參數(shù)資料

| 型號: | XRT16C854 |

| 廠商: | Exar Corporation |

| 英文描述: | 2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO |

| 中文描述: | 2.97V至5.5V四路UART的128字節(jié)FIFO |

| 文件頁數(shù): | 31/54頁 |

| 文件大小: | 485K |

| 代理商: | XRT16C854 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

xr

REV. 3.0.1

XR16C854/854D

2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO

31

LCR[3]: TX and RX Parity Select

Parity or no parity can be selected via this bit. The parity bit is a simple way used in communications for data

integrity check. See

Table 12

for parity selection summary below.

Logic 0 = No parity.

Logic 1 = A parity bit is generated during the transmission while the receiver checks for parity error of the

data character received.

LCR[4]: TX and RX Parity Select

If the parity bit is enabled with LCR bit-3 set to a logic 1, LCR BIT-4 selects the even or odd parity format.

Logic 0 = ODD Parity is generated by forcing an odd number of logic 1’s in the transmitted character. The

receiver must be programmed to check the same format (default).

Logic 1 = EVEN Parity is generated by forcing an even number of logic 1’s in the transmitted character. The

receiver must be programmed to check the same format.

LCR[5]: TX and RX Parity Select

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5 = logic 0, parity is not forced (default).

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 0, parity bit is forced to a logical 1 for the transmit and receive

data.

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 1, parity bit is forced to a logical 0 for the transmit and receive

data.

LCR[6]: Transmit Break Enable

When enabled, the Break control bit causes a break condition to be transmitted (the TX output is forced to a

“space’, logic 0, state). This condition remains, until disabled by setting LCR bit-6 to a logic 0.

Logic 0 = No TX break condition (default).

Logic 1 = Forces the transmitter output (TX) to a “space”, logic 0, for alerting the remote receiver of a line

break condition.

LCR[7]: Baud Rate Divisors Enable

Logic 0 = Data registers are selected (default).

Logic 1 = Divisor latch registers are selected.

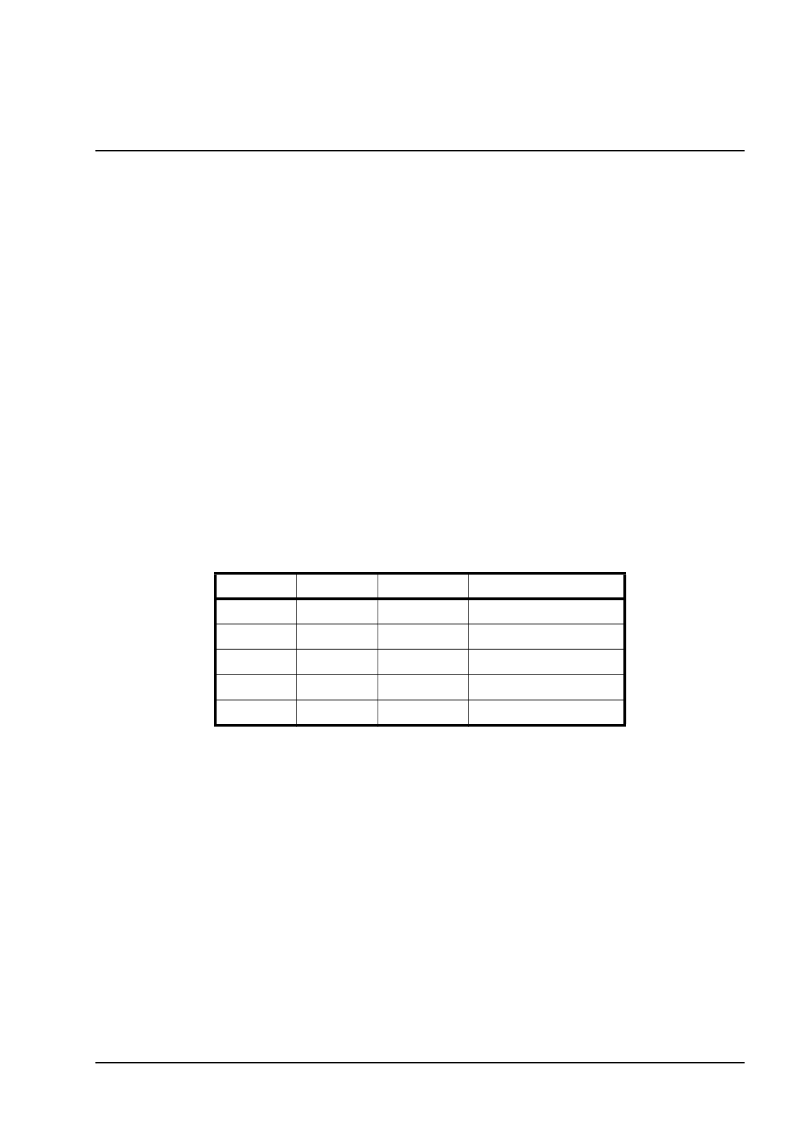

T

ABLE

12: P

ARITY

SELECTION

LCR B

IT

-5

LCR B

IT

-4

LCR B

IT

-3

P

ARITY

SELECTION

X

X

0

No parity

0

0

1

Odd parity

0

1

1

Even parity

1

0

1

Force parity to mark, “1”

1

1

1

Forced parity to space, “0”

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT16L2552 | 2.25V TO 5.5V DUART WITH 16-BYTE FIFO |

| XRT3591 | SINGLECHIP V. 35 TRANSCEIVER |

| XRT3591B | SINGLECHIP V. 35 TRANSCEIVER |

| XRT3591BID | SINGLECHIP V. 35 TRANSCEIVER |

| XRT3591BIP | SINGLECHIP V. 35 TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT16L2552 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.25V TO 5.5V DUART WITH 16-BYTE FIFO |

| XRT2588CN | 制造商:Exar Corporation 功能描述: |

| XR-T2713CP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Subscriber Line Metering/Monitoring Circuit |

| XR-T3588 | 制造商:EXAR 制造商全稱:EXAR 功能描述:V.35 Interface Receiver/Transmitter |

| XR-T3588-89ES | 制造商:EXAR 制造商全稱:EXAR 功能描述:XR-T3588/89 Evaluation System |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。