- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16512 > XR17C152CM-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17C152 100TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XR17C152CM-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 27/62頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17C152 100TQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

á

XR17C152

REV. 1.2.0

5V PCI BUS DUAL UART

33

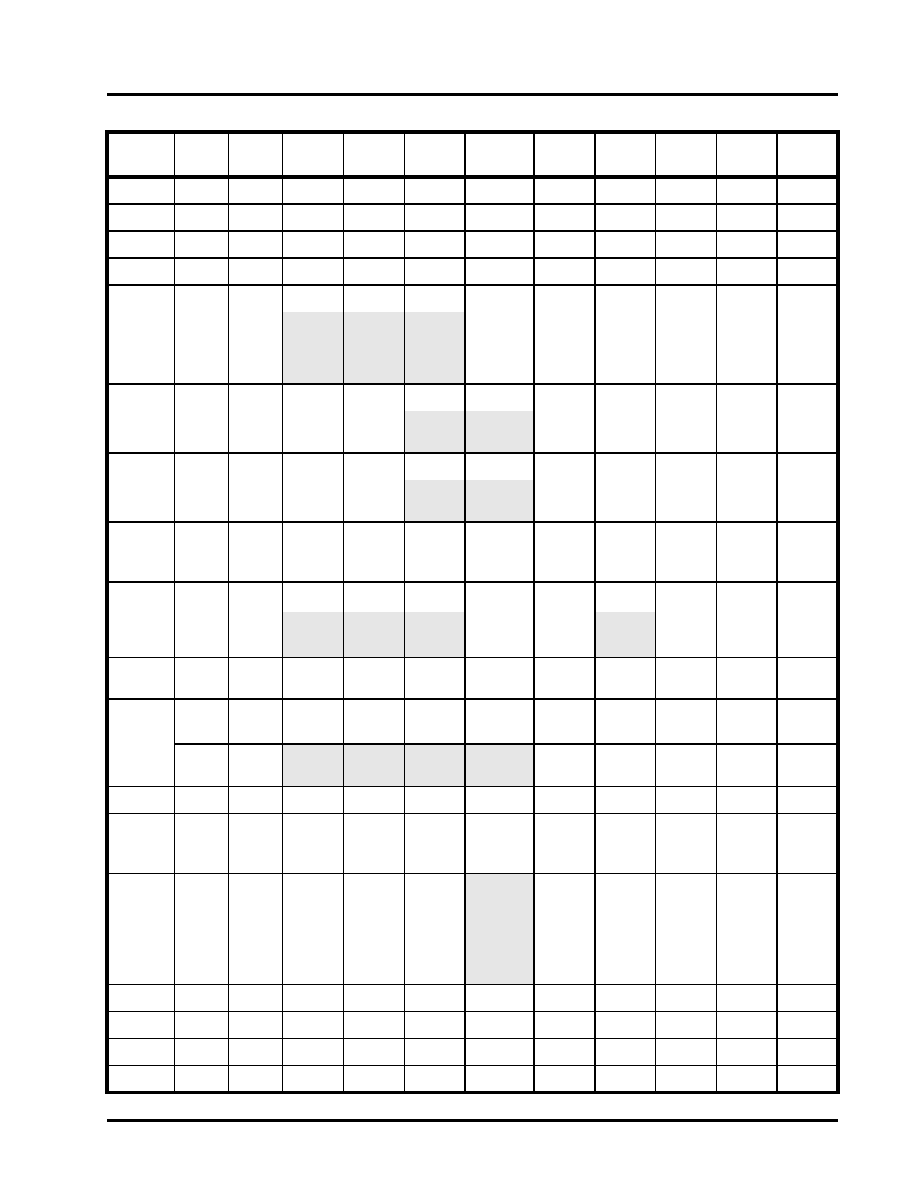

TABLE 12: UART CHANNEL CONFIGURATION REGISTERS DESCRIPTION. SHADED BITS ARE ENABLED BY EFR BIT-4.

ADDRESS

A3-A0

REG

NAME

READ/

WRITE

BIT-7

BIT-6

BIT-5

BIT-4

BIT-3

BIT-2

BIT-1

BIT-0

COMMENT

0 0 0 0

RHR

R

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

LCR[7]=0

0 0 0 0

THR

W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

LCR[7]=0

0 0 0 0

DLL

R/W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

LCR[7]=1

0 0 0 1

DLM

R/W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

LCR[7]=1

0 0 0 1

IER

R/W

0/

0

Modem

Status Int.

Enable

RX Line

Status Int.

Enable

TX Empty

Int.

Enable

RX Data

Int.

Enable

CTS/

DSR# Int.

Enable

RTS/

DTR# Int.

Enable

Xon/Xoff/

Sp. Char.

Int.

Enable

0 0 1 0

ISR

R

FIFOs

Enable

FIFOs

Enable

0/

INT

Source

Bit-3

INT

Source

Bit-2

INT

Source

Bit-1

INT

Source

Bit-0

Delta-

Flow Cntl

Xoff/spe-

cial char

0 0 1 0

FCR

W

RX FIFO

Trigger

RX FIFO

Trigger

0/

DMA

Mode

TX FIFO

Reset

RX FIFO

Reset

FIFOs

Enable

TX FIFO

Trigger

TX FIFO

Trigger

0 0 1 1

LCR

R/W

Divisor

Enable

Set TX

Break

Set Parity Even Par-

ity

Parity

Enable

Stop Bits

Word

Length

Bit-1

Word

Length

Bit-0

0 1 0 0

MCR

R/W

0/

Internal

Lopback

Enable

(OP2)1

(OP1)1

RTS# Pin

Control

DTR# Pin

Control

BRG

Prescaler

IR

Enable

XonAny

RTS/DTR

Flow Sel

0 1 0 1

LSR

R/W

RX FIFO

ERROR

TSR

Empty

THR

Empty

RX Break

RX Fram-

ing Error

RX Parity

Error

RX Over-

run

RX Data

Ready

0 1 1 0

MSR

R

CD

RI

DSR

CTS

Delta

CD#

Delta

RI#

Delta

DSR#

Delta

CTS#

MSR

W

RS485

DLY-3

RS485

DLY-2

RS485

DLY-1

RS485

DLY-0

Reserved Reserved Reserved Reserved

0 1 1 1

SPR

R/W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

User Data

1 0 0 0

FCTR

R/W

TRG

Table

Bit-1

TRG

Table

Bit-0

Auto

RS485

Enable

Invert IR

RX Input

RTS/DTR

Hyst Bit-3

RTS/DTR

Hyst Bit-2

RTS/DTR

Hyst Bit-1

RTS/DTR

Hyst Bit-0

1 0 0 1

EFR

R/W

Auto

CTS/DSR

Enable

Auto

RTS/DTR

Enable

Special

Char

Select

Enable

IER [7:5],

ISR [5:4],

FCR[5:4],

MCR[7:5,2]

MSR[7:4]

Software

Flow Cntl

Bit-3

Software

Flow Cntl

Bit-2

Software

Flow Cntl

Bit-1

Software

Flow Cntl

Bit-0

1 0 1 0

TXCNT

R

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 0 1 0

TXTRG

W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 0 1 1

RXCNT

R

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 0 1 1

RXTRG

W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-J52-EX | CONVERTER MOD DC/DC 15V 75W |

| SI3056SSI2-EVB | BOARD EVAL SI3056/SI3010 SSI |

| 6828281-2 | CA 62.5 SC DUP-MTRJ OR SECURE |

| RHS0E152MCN1GS | CAP ALUM 1500UF 2.5V 20% SMD |

| RBM15DTKD-S288 | CONN EDGECARD 30POS .156 EXTEND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17C152CM-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C152IM | 制造商:EXAR 制造商全稱:EXAR 功能描述:5V PCI BUS DUAL UART |

| XR17C152IM-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C154 | 制造商:EXAR 制造商全稱:EXAR 功能描述:5V PCI BUS QUAD UART |

| XR17C154_05 | 制造商:EXAR 制造商全稱:EXAR 功能描述:5V PCI BUS QUAD UART |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。