- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300083 > V59C1G01408QAJ37E (PROMOS TECHNOLOGIES INC) 256M X 4 DDR DRAM, 0.5 ns, PBGA68 PDF資料下載

參數(shù)資料

| 型號: | V59C1G01408QAJ37E |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | 256M X 4 DDR DRAM, 0.5 ns, PBGA68 |

| 封裝: | ROHS COMPLIANT, FBGA-68 |

| 文件頁數(shù): | 49/79頁 |

| 文件大小: | 1029K |

| 代理商: | V59C1G01408QAJ37E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁

53

ProMOS TECHNOLOGIES

V59C1G01(408/808/168)QA

V59C1G01(408/808/168)QA Rev. 1.2 April 2008

No Operation Command

The No Operation Command should be used in cases when the SDRAM is in a idle or a wait state. The pur-

pose of the No Operation Command is to prevent the SDRAM from registering any unwanted commands

between operations. A No Operation Command is registered when CS is low with RAS, CAS, and WE held

high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is

still executing, such as a burst read or write cycle.

Deselect Command

The Deselect Command performs the same function as a No Operation Command. Deselect Command

occurs when CS is brought high, the RAS, CAS, and WE signals become don’t care.

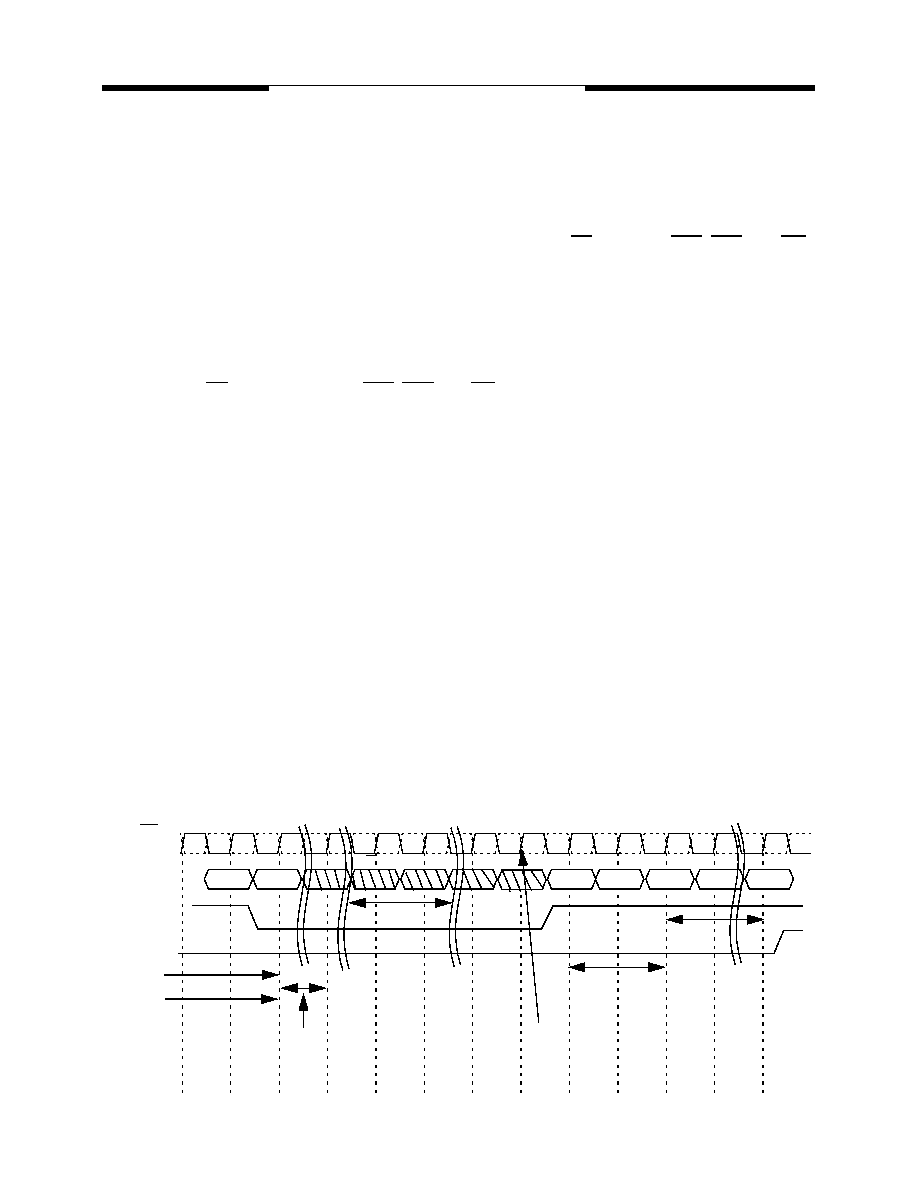

Input Clock Frequency Change

During operation the DRAM input clock frequency can be changed under the following conditions:

a) During Self-Refresh operation

b) DRAM is in precharged power-down mode and ODT is completely turned off.

The DDR2-SDRAM has to be in precharged power-down mode and idle. ODT must be allready turned off and

CKE must be at a logic “l(fā)ow” state. After a minimum of two clock cycles after tRP and tAOFD have been sat-

isfied the input clock frequency can be changed. A stable new clock frequency has to be provided, before

CKE can be changed to a “high” logic level again. After tXP has been satisfied a DLL RESET command via

EMRS has to be issued. During the following DLL re-lock period of 200 clock cycles, ODT must remain off.

After the DLL-re-lock period the DRAM is ready to operate with the new clock frequency.

CK

CKE

T0

T4

Tx+1

Ty

Ty+1

Ty+2

T1

T2

Tx

CK

Valid

DLL

NOP

200 Clocks

Frequency Change

Ty+3

Tz

NOP

RESET

tRP

Clock Frequency Change in Precharge Power Down Mode

tXP

Occurs here

tAOFD

Stable new clock

before power down exit

ODT is off during

DLL RESET

Minmum 2 clocks

required before

changing frequency

ODT

RAS, CS

CAS, WE

Ty+4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V59C1G01408QAJ37I | 256M X 4 DDR DRAM, 0.5 ns, PBGA68 |

| V5D010EB4D | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.5A, 125VDC, 4.4mm, PANEL MOUNT |

| V5F110CB | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, PANEL MOUNT |

| V5PNF | CABLE TERMINATED, FEMALE, N CONNECTOR, THREAD-IN STUB SELF-FLARE |

| V5T110TB3 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.6A, 125VDC, 2.4mm, PANEL MOUNT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4E | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。