- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄199479 > TSB43AA82GGW (TEXAS INSTRUMENTS INC) 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PBGA176 PDF資料下載

參數(shù)資料

| 型號: | TSB43AA82GGW |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PBGA176 |

| 封裝: | PLASTIC, BGA-176 |

| 文件頁數(shù): | 120/146頁 |

| 文件大小: | 770K |

| 代理商: | TSB43AA82GGW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁當(dāng)前第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁

49

Table 4-8. Generic Receive Format Descriptions (Continued)

FIELD NAME

DESCRIPTION

quadlet data

For write requests and read responses, this field holds the transferred data. For write responses and read requests, this field

is not present.

data_length

For write requests, read responses, and locks, this field indicates the number of bytes being transferred. For read requests,

this field indicates the number of bytes of data to be read. A write-response packet does not use this field.

Note: The number of bytes does not include the header, only the bytes of block data.

extended_tCode

The block extended_tCode to be performed on the data in this packet. See Table 6-10 of the IEEE 1394-1995 standard.

block data

For write requests and read responses, this field holds the transferred data. For write responses and read requests, this field

is not present.

4.5

Management and Command FIFOs (MTQ/CTQ and MRF/CRF)

MTQ/CTQ transmit refers to the use of the MTQ/CTQ interface. Packet transmission with MTQ/CTQ appears with

the format shown in Section 4.5.1. As with other packet transmissions, it is accessed through the CFR (70h-78h).

The tLabel and the tCode attached to a packet direct each request and response packet to the appropriate FIFO. A

response packet needs to have the same tLabel as its request packet. With this rule, TSB43AA82 assigns the

response packet from the initiator to each receive FIFO.

4.5.1

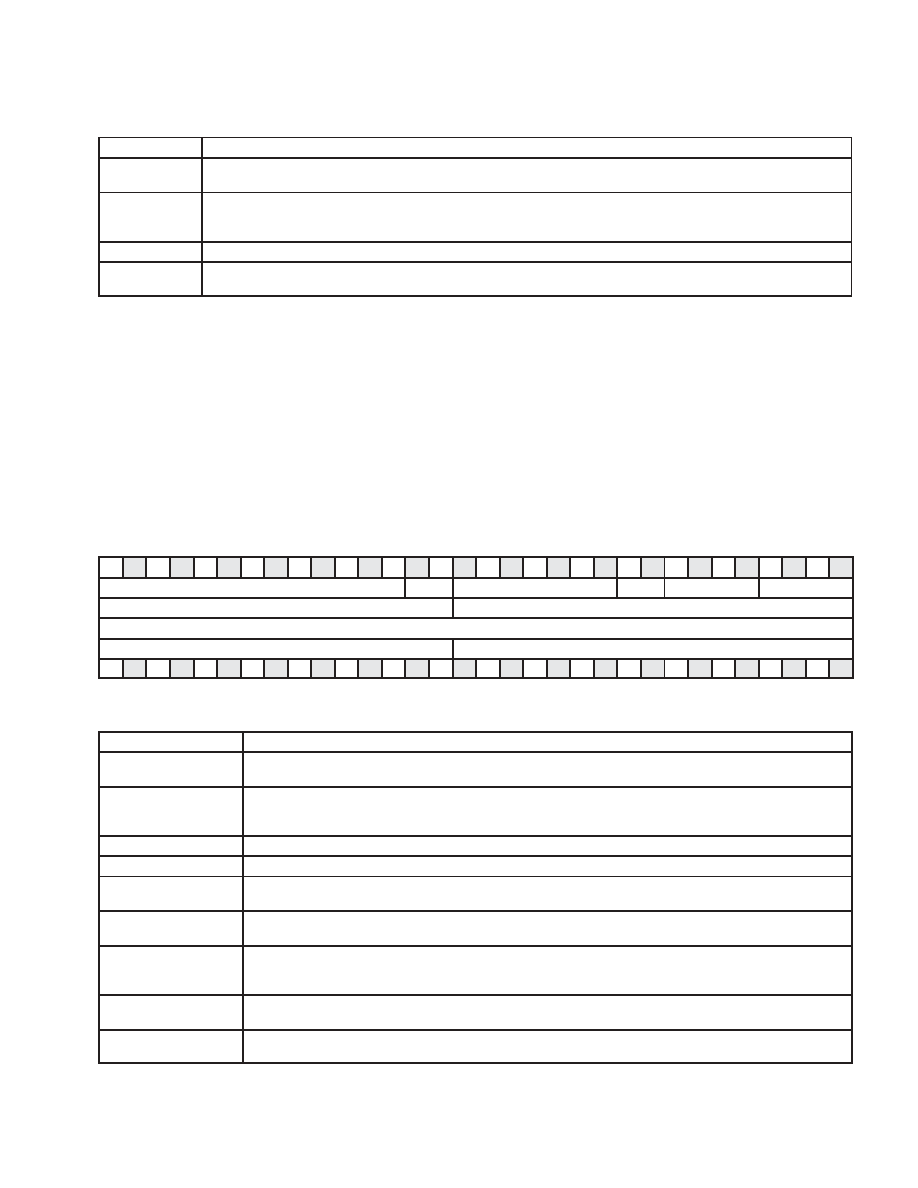

MTQ/CTQ Format

Packets transmitted from the MTQ/CTQ are in the same format as a read request block transmit to the ATF. However,

as stated in Section 4.2.1, this must be a block read request with the specified tLabel. The block-transmit format is

shown in Figure 411 and field descriptions are shown in Table 49. The first quadlet contains packet control

information. The second and third quadlets contain the 64-bit, quadlet-aligned address. The data_length of a packet

transmitted from MTQ should be set to 32 bytes.

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Reserved

spd

tLabel

rt

tCode

prior

destination ID

destination_offset_high

destination_offset_low

data_length

extended_tCode

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Figure 411. MTQ/CTQ Transmission Block Read Packet Format

Table 49. Block-Transmit Format Descriptions

FIELD NAME

DESCRIPTION

spd

This field indicates the speed at which this packet is to be sent. 00 = 100 Mbps, 01 = 200 Mbps, and 10 = 400 Mbps,

and 11 is undefined for this implementation.

tLabel

This field is the transaction label, which is a unique tag for each outstanding transaction between two nodes. This is

used to pair up a response packet with its corresponding request packet. When using the MTQ, tLabel must be set to

10_xxxx. When using the CTQ, tLabel must be set to 11_xxxx.

rt

The retry code for this packet is 00 = new, 01 = retry_X, 10 = retryA, and 11 = retryB.

tCode

tCode is the transaction code for this packet (see Table 6-9 of IEEE 1394-1995 standard).

prior

The priority level for this packet. For cable implementation, the value of the bits must be zero. For backplane

implementation, see clause 5.4.1.3 and 5.4.2.1 of the IEEE 1394-1995 standard.

destination ID

This is the concatenation of the 10-bit bus number and the 6-bit node number that forms the node address to which

this packet is being sent.

destination_offset_high,

destination_offset_low

The concatenation of these two fields addresses a quadlet in the destination node address space. This address must

be quadlet aligned (modulo 4). The upper four bits of the destination_offset_high field are used as the response code

for lock-response packets and the remaining bits are reserved.

data_length

The number of bytes of data to be transmitted in the packet. The data_length of packet transmitted from MTQ must be

set to 32 bytes.

extended_tCode

The block extended_tCode to be performed on the data in this packet. See Table 6-10 of the IEEE 1394-1995

standard.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB43DA42GHCR | PCI BUS CONTROLLER, PBGA196 |

| TSB500SK02 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| TSB500SK10MDS | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| TSB5000331DS | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| TSB5000831 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB43AA82GHH | 制造商:Texas Instruments 功能描述: |

| TSB43AA82I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1394 INTEGRATED PHY AND LINK LAYER CONTROLLER |

| TSB43AA82IGGW | 功能描述:1394 接口集成電路 2Port Hi Perf Integ Phy&Link Layer Chip RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB43AA82PGE | 功能描述:1394 接口集成電路 2Port Hi Perf Integ Phy&Link Layer Chip RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB43AA82PGEG4 | 功能描述:1394 接口集成電路 2Port Hi Per Int Phy & Link Layer Chip RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。