- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225036 > RG82870P2 Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號(hào): | RG82870P2 |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項(xiàng)-數(shù)據(jù)表參考 |

| 文件頁(yè)數(shù): | 79/157頁(yè) |

| 文件大?。?/td> | 1407K |

| 代理商: | RG82870P2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)當(dāng)前第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)

Intel

82845MP/82845MZ Chipset-Mobile (MCH-M)

28

Datasheet

250687-002

R

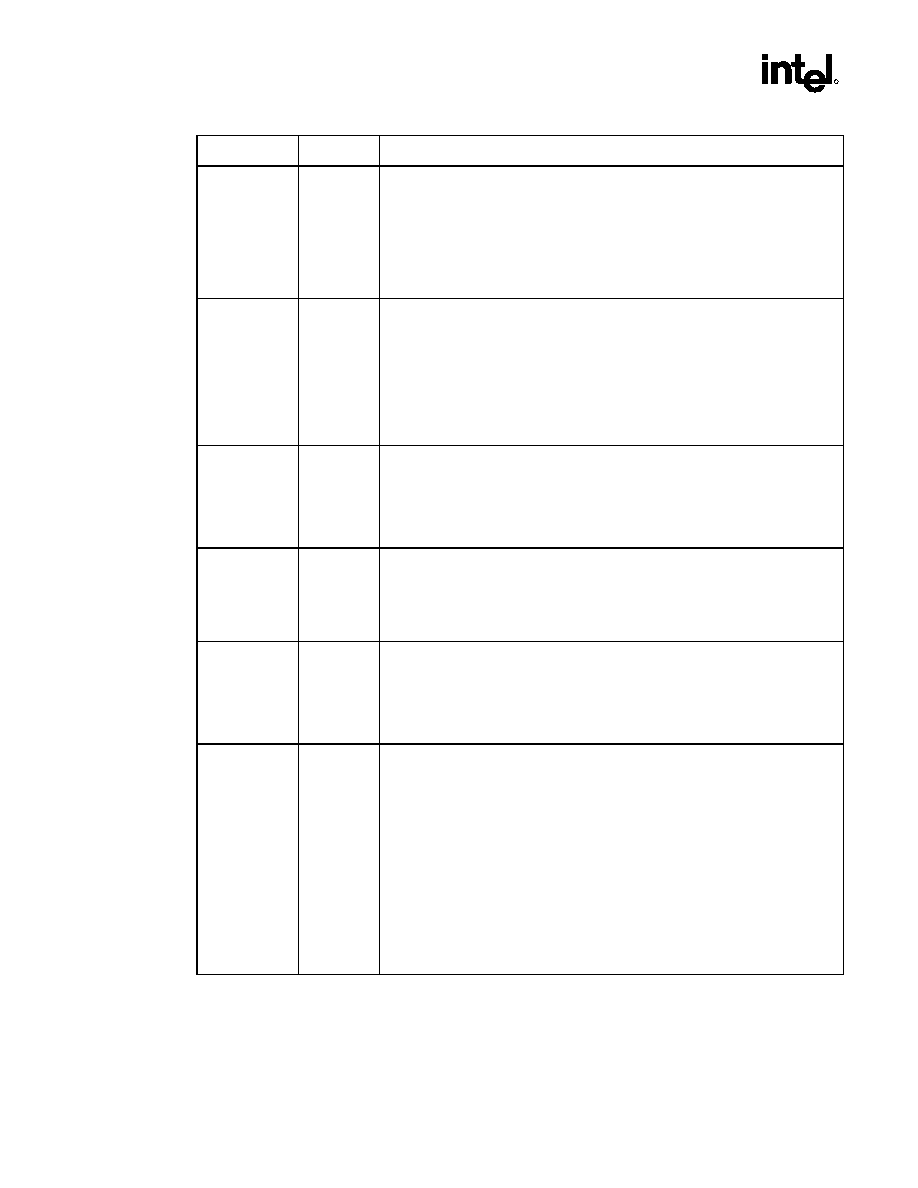

Signal Name

Type

Description

G_STOP#

I/O

s/t/s

AGP

G_STOP#: Stop

During PIPE# and SBA Operation: This signal is not used during PIPE# or SBA

operation.

During FRAME# Operation: G_STOP# is an input when the MCH-M acts as a

FRAME#-based AGP initiator and is an output when the MCH-M acts as a

FRAME#-based AGP target. G_STOP# is used for disconnect, retry, and abort

sequences on the AGP interface

G_DEVSEL#

I/O

s/t/s

AGP

G_ DEVSEL#: Device Select

During PIPE# and SBA Operation: This signal is not used during PIPE# or SBA

operation.

During FRAME# Operation: G_DEVSEL#, when asserted, indicates that a

FRAME#-based AGP target device has decoded its address as the target of the

current access. The MCH-M asserts G_DEVSEL# based on the SDRAM address

range being accessed by a PCI initiator. As an input, G_DEVSEL# indicates

whether the AGP master has recognized a PCI cycle to it.

G_REQ#

I

AGP

G_REQ#: Request

During SBA Operation: This signal is not used during SBA operation.

During PIPE# and FRAME# Operation: G_REQ#, when asserted, indicates that

the AGP master is requesting use of the AGP interface to run a FRAME#- or

PIPE#-based operation.

G_GNT#

O

AGP

G_GNT#: Grant

During SBA, PIPE# and FRAME# Operation: G_GNT#, along with the

information on the ST[2:0] signals (status bus), indicates how the AGP interface will

be used next. Refer to the AGP Interface Specification, Revision 2.0 for further

explanation of the ST[2:0] values and their meanings.

G_AD[31:0]

I/O

AGP

G_AD[31:0]: Address/Data Bus

During PIPE# and FRAME# Operation: The G_AD[31:0] signals are used to

transfer both address and data information on the AGP interface.

During SBA Operation: The G_AD[31:0] signals are used to transfer data on the

AGP interface.

G_CBE[3:0]#

I/O

AGP

Command/Byte Enable

During FRAME# Operation: During the address phase of a transaction, the

G_CBE[3:0]# signals define the bus command. During the data phase, the

G_CBE[3:0]# signals are used as byte enables. The byte enables determine which

byte lanes carry meaningful data. The commands issued on the G_CBE# signals

during FRAME#-based AGP transactions are the same G_CBE# command

described in the PCI 2.2 specification.

During PIPE# Operation: When an address is enqueued using PIPE#, the C/BE#

signals carry command information. Refer to the AGP 2.0 Interface Specification,

Revision 2.0 for the definition of these commands. The command encoding used

during PIPE#-based AGP is different than the command encoding used during

FRAME#-based AGP cycles (or standard PCI cycles on a PCI bus).

During SBA Operation: These signals are not used during SBA operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RH5RE36AA-T1-FA | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PSSO3 |

| RH5RE56AA-T1-FA | 5.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PSSO3 |

| RE5RE36AA-TZ-FC | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PBCY3 |

| RE5RE36AC-TZ-FC | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PBCY3 |

| RE5RE56AA-TZ-FC | 5.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PBCY3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RG82870P2 S L675 | 制造商:Intel 功能描述:Interface, Dual-Channel Ddr200 Memory Interface For Up To 3.2 Gb/S Memory Bandwidth |

| RG82870P2 S L6SU | 制造商:Intel 功能描述:INTERFACE, DUAL-CHANNEL DDR200 MEMORY INTERFACE FOR UP TO 3.2 GB/S MEMORY BANDWIDTH |

| RG82870P2 SL6SU | 制造商:Intel 功能描述: |

| RG-8B-96-110V | 制造商:TRUMETER COMPANY INC 功能描述:Power Factor Controller |

| RG-8BS-96-110V | 制造商:TRUMETER COMPANY INC 功能描述:Power Factor Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。