- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225036 > RG82845MP Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號(hào): | RG82845MP |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項(xiàng)-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 96/157頁 |

| 文件大小: | 1407K |

| 代理商: | RG82845MP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁當(dāng)前第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁

Intel

82845MP/82845MZ Chipset-Mobile (MCH-M)

250687-002

Datasheet

43

R

3.6.1.

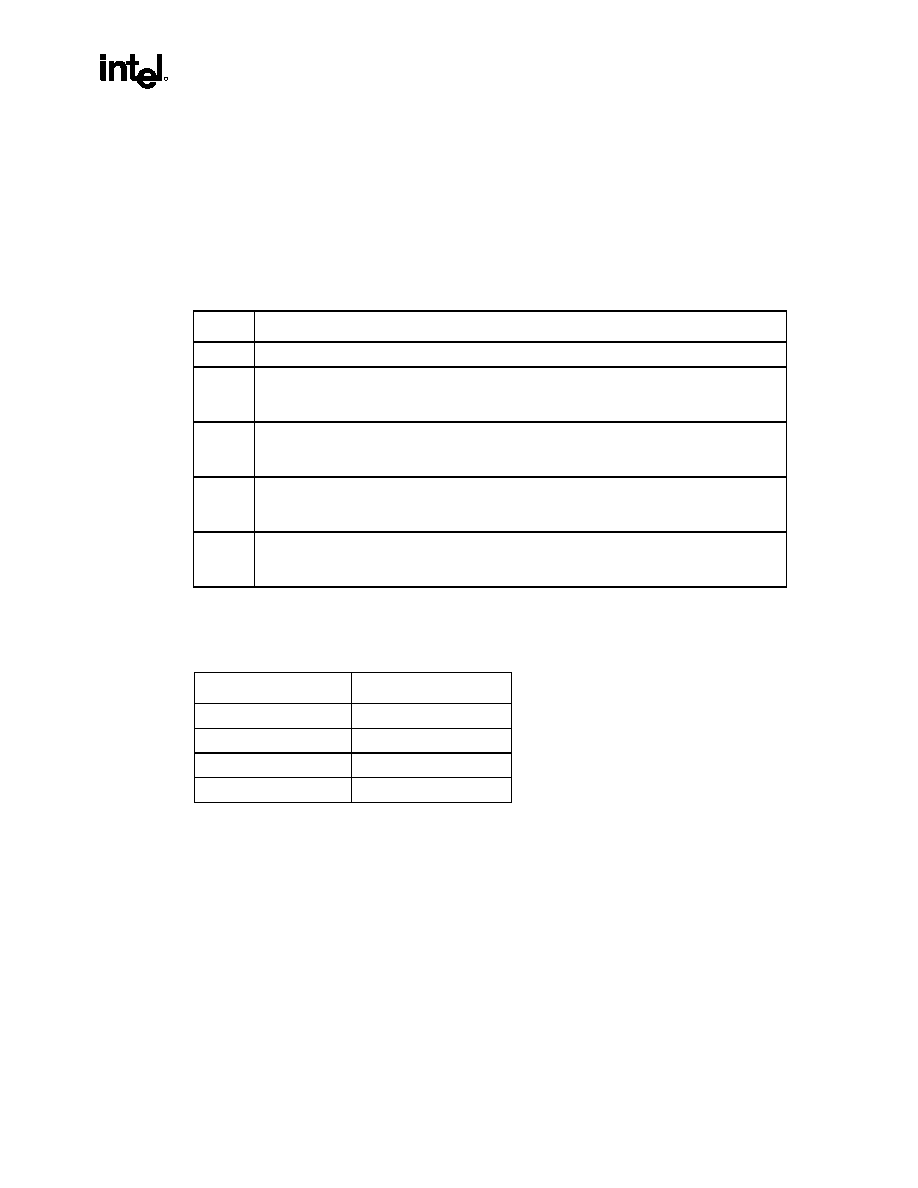

DRAMWIDTH—DRAM Width Register

Address Offset:

2Ch

Default Value:

00h

Access:

R/W

Size:

8 bits

This register determines the width of SDRAM devices populated in each row of memory.

Bit

Descriptions

7:4

Reserved.

3

Row 3 Width. Width of devices in Row 3

0 = 16-bit wide devices, or Unpopulated (default)

1 = 8-bit wide devices

2

Row 2 Width. Width of devices in Row 2

0 = 16-bit wide devices, or Unpopulated (default)

1 = 8-bit wide devices

1

Row 1 Width. Width of devices in Row 1

0 = 16-bit wide devices, or Unpopulated (default)

1 = 8-bit wide devices

0

Row 0 Width. Width of devices in Row 0

0 = 16-bit wide devices, or Unpopulated (default)

1 = 8-bit wide devices

Note: Since there are multiple clock signals assigned to each row of a DIMM, it is important to clarify exactly

which row width field affects which clock signal.

Row Parameters

DDR Clocks Affected

0

SCK[2:0]/SCK[2:0]#

1

SCK[2:0]/SCK[2:0]#

2

SCK[5:3]/SCK[5:3]#

3

SCK[5:3]/SCK[5:3]#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RG82845MZ | Controller Miscellaneous - Datasheet Reference |

| RG82870P2 | Controller Miscellaneous - Datasheet Reference |

| RH5RE36AA-T1-FA | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PSSO3 |

| RH5RE56AA-T1-FA | 5.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PSSO3 |

| RE5RE36AA-TZ-FC | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PBCY3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RG82845MP S L66J | 制造商:Intel 功能描述:Chipset Memory Controller Hub Mobile 593-Pin FCBGA |

| RG82845MZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| RG82845PE S L6H5 | 制造商:Intel 功能描述:CHIPSTGMCH 82845PE HT-PBGA760 |

| RG82845PESL6Q3 | 制造商:Intel 功能描述:Chipsets |

| RG82845-SL5V7 | 制造商:Intel 功能描述:INTEL 845G GRAPHICS AND MEMORY CONTROLLER HUB(GMCH) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。