- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370013 > PowerPC 440 (IBM Microeletronics) 32-bit RISC PowerPC Embedded Processor Cores(32位 RISC PowerPC 嵌入式處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | PowerPC 440 |

| 廠(chǎng)商: | IBM Microeletronics |

| 英文描述: | 32-bit RISC PowerPC Embedded Processor Cores(32位 RISC PowerPC 嵌入式處理器) |

| 中文描述: | 32位RISC PowerPC嵌入式處理器內(nèi)核(RISC的32位的PowerPC嵌入式處理器) |

| 文件頁(yè)數(shù): | 14/18頁(yè) |

| 文件大小: | 317K |

| 代理商: | POWERPC 440 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

PowerPC 440 Core

09/21/1999

Page 14 of 18

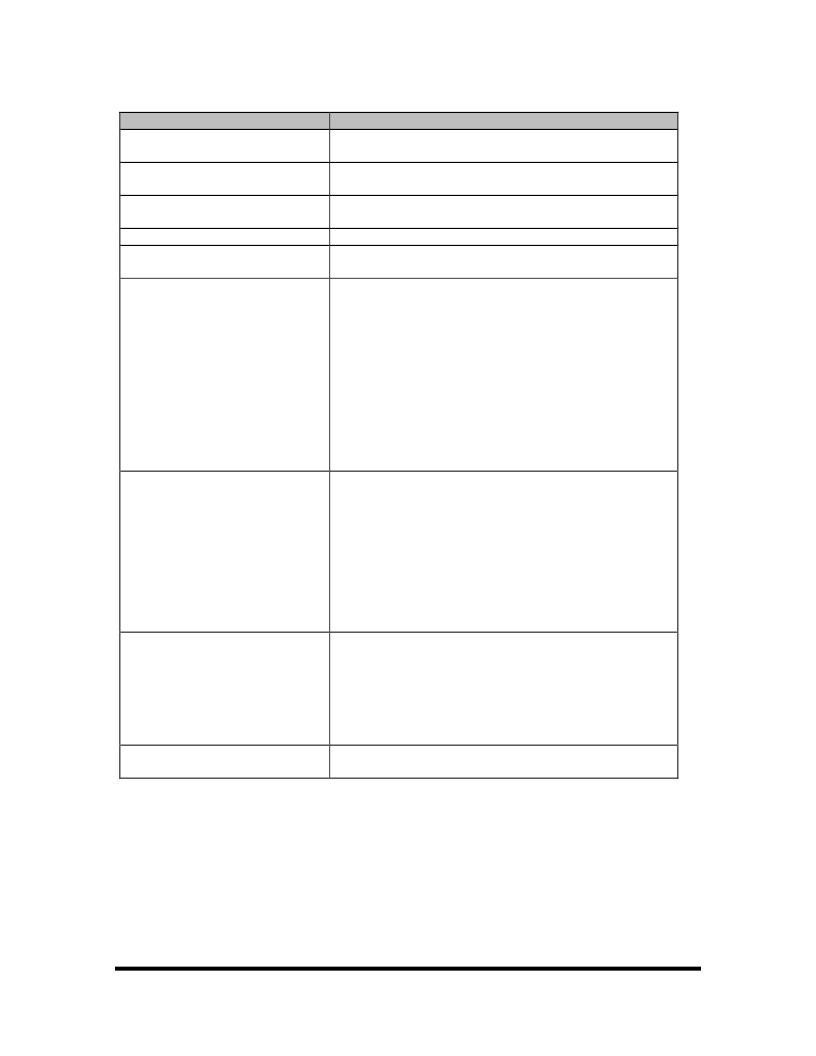

Debug Event

Description

Branch Taken

A Branch Taken debug event occurs prior to the execution of

a taken branch instruction.

The Instruction Completion debug event occurs after the

completion of any instruction.

The Return From Interrupt debug event occurs after the

completion of an rfi or rfci instruction.

The Interrupt debug event occurs after an interrupt is taken.

The Trap debug event occurs prior to the execution of a trap

instruction, where the trap condition is met.

The IAC debug event occurs prior to the execution of an

instruction at an address that matches the contents of one of

four IAC registers (IAC1, IAC2, IAC3, and IAC4).

Instruction Completion

Return from Interrupt

Interrupt

Trap

Instruction Address Compare (IAC)

Alternatively, the registers can be combined to cause an IAC

debug event prior to the execution of an instruction at an

address contained in one of the following ranges as specified

by the four IAC registers:

IAC1 <= range < IAC2 (inclusive),

IAC3 <= range < IAC4 (inclusive),

range low < IAC1 < IAC2 <= range high (exclusive), or

range low < IAC3 < IAC4 <= range high (exclusive).

The DAC debug event occurs prior to the execution of an

instruction that accesses a data address matching the contents

of one of the two DAC registers (DAC1 and DAC2).

Data Address Compare (DAC)

Alternatively, the registers can be combined to cause a DAC

debug event occurs prior to the execution of an instruction

that accesses a data address within one of the following

ranges specified by the two DAC registers:

DAC1 <= range < DAC2 (inclusive), or

range low < DAC1 < DAC2 <= range high (exclusive).

The Data Value Compare debug event occurs prior to the

execution of an instruction that accesses a data address

matching one of the two DAC registers (or within a DAC

range) and containing a particular data value as specified by

one of the two DVC registers. The DVC debug event may

occur when a selected data byte, half-word or word matches

the corresponding element in DVC1 or DVC2.

An unconditional debug event is set by a debug tool through

the JTAG port or by ASIC logic external to the PPC440.

Data Value Compare (DVC)

Unconditional Event

Table 4 - Debug Events

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PowerPC 602 | 32-bit implementation Reduced Instruction Set Computer (RISC) Microprocessors.(32位精簡(jiǎn)指令集微處理器) |

| PowerPC 603e | 32-Bit PowerPC Reduced Instruction Set Computer (RISC) Microprocessor(32-位 PowerPC 精簡(jiǎn)指令集微處理器) |

| PowerPC EM603e | 32-Bit PowerPC Reduced Instruction Set Computer (RISC) Microprocessor(32-位 PowerPC 精簡(jiǎn)指令集微處理器) |

| PowerPC 740 | 32-Bit Embedded Microprocessor(32位精簡(jiǎn)指令集嵌入式微處理器) |

| PowerPC 750CX | 32-Bit Reduced Instruction Set Computer (RISC) Microprocessors(32位精簡(jiǎn)指令集微處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| POWERPLUG15W | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

| POWERPLUG24W | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

| POWERPLUS 2C 2500MAH | 制造商:Energizer Battery Company 功能描述: |

| POWERPLUS 2D 2500MAH | 制造商:Energizer Battery Company 功能描述: |

| POWERPLUS 4AAA 850MAH | 制造商:Energizer Battery Company 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。