- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT90221 (Mitel Networks Corporation) Quad IMA/UNI PHY Device(四端口 IMA/UNI 物理層設備(四端口ATM IMA和UNI處理器)) PDF資料下載

參數(shù)資料

| 型號: | MT90221 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Quad IMA/UNI PHY Device(四端口 IMA/UNI 物理層設備(四端口ATM IMA和UNI處理器)) |

| 中文描述: | 四IMA的/單向物理層設備(IMA的四端口/單向物理層設備(四端口自動柜員機IMA的和單向處理器)) |

| 文件頁數(shù): | 69/116頁 |

| 文件大小: | 309K |

| 代理商: | MT90221 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁當前第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

MT90221

61

7.7

RX Delay Registers Description

Tables 65 to 74 describe the

RX Delay

registers.

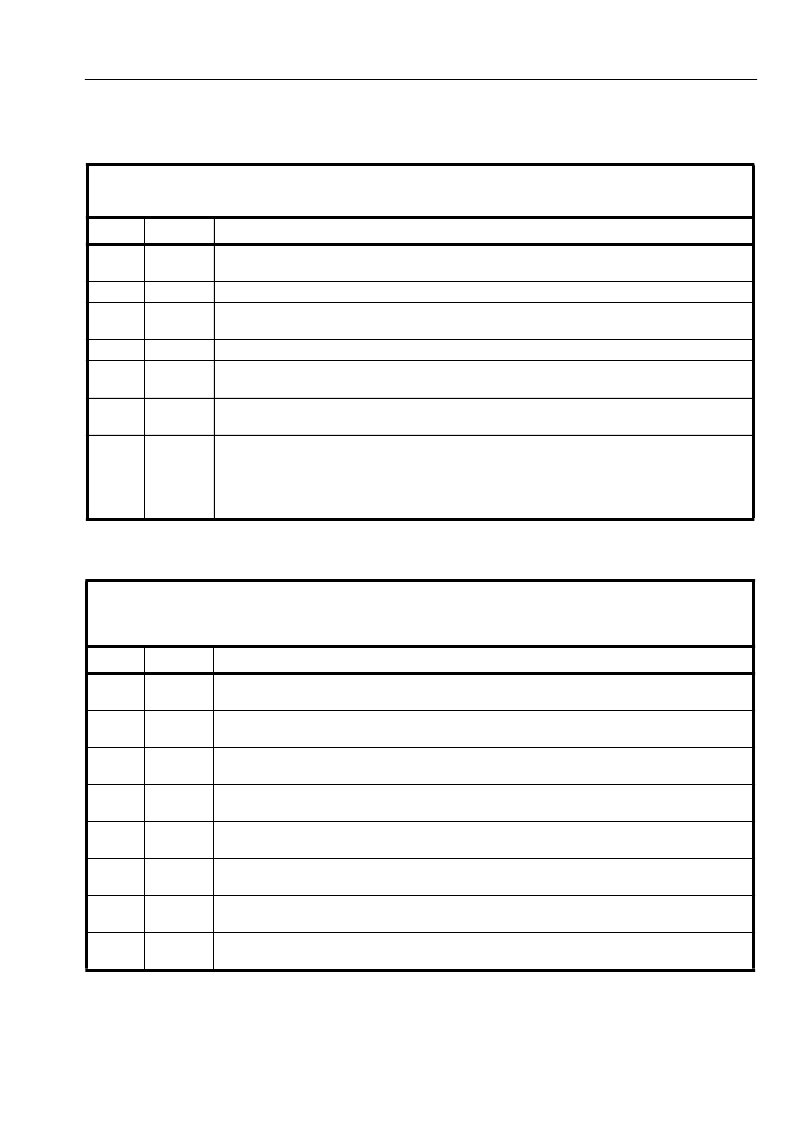

Address (Hex):

Synchronized access

Reset Value (Bin):

280

1X000000

Bit #

Type

Description

7

R

Upon a write to this register, the bit will go to 0 and will return to 1 when the transfer is

completed

Toggle Bit.

Write 0 to initiate a transfer from the MT90221 registers to the external RAM.

Write 1 to initiate a transfer from the external RAM to the MT90221 registers.

Reserved, write 0 for normal operation.

When Test Mode bit is 1; write 1 to enable the direct addressing mode to the External

SRAM.

When Test Mode bit is 1; write 0 for normal operation.Write 1 for disabling all access to

the external RAM except for the uP port (for RAM test purposes)

When bit 1 is 1, there is no access to the external RAM (no reset or read or write action to

the external RAM is done).

When bit 1 is 0 and bit 0 is 0, then the external RAM is initialized.

When bit 1 is 0 and bit 0 is 1, then a read or write access to the external RAM is

performed, as defined by bit 5.

6

5

R

R/W

4

3

R/W

R/W

2

R/W

1:0

R/W

Table 65 - RX External SRAM Control Register

Address (Hex):

Direct access

281

Used to increment or decrement the recombiner delay for an IMA Group.

The value is in the Guardband/Delta Delay register

00

Reset Value (Hex):

Bit #

Type

Description

7

R/W

Write a 1 to decrement the recombiner delay of IMA Group #3. The bit will return to 0

when the delay is adjusted. Writing a 0 has no effect.

Write a 1 to increment the recombiner delay of IMA Group #3. The bit will return to 0 when

the delay is adjusted. Writing a 0 has no effect.

Write a 1 to decrement the recombiner delay of IMA Group #2. The bit will return to 0

when the delay is adjusted. Writing a 0 has no effect.

Write a 1 to increment the recombiner delay of IMA Group #2. The bit will return to 0 when

the delay is adjusted. Writing a 0 has no effect.

Write a 1 to decrement the recombiner delay of IMA Group #1. The bit will return to 0

when the delay is adjusted. Writing a 0 has no effect.

Write a 1 to increment the recombiner delay of IMA Group #1. The bit will return to 0 when

the delay is adjusted. Writing a 0 has no effect.

Write a 1 to decrement the recombiner delay of IMA Group #0. The bit will return to 0

when the delay is adjusted. Writing a 0 has no effect.

Write a 1 to increment the recombiner delay of IMA Group #0. The bit will return to 0 when

the delay is adjusted. Writing a 0 has no effect.

6

R/W

5

R/W

4

R/W

3

R/W

2

R/W

1

R/W

0

R/W

Table 66 - Increment/Decrement Delay Control Register

相關PDF資料 |

PDF描述 |

|---|---|

| MT90401 | SONET/SDH System Synchronizer(SONET/SDH 系統(tǒng)同步裝置(由一個數(shù)字鎖相環(huán)組成)) |

| MT9040 | T1/E1 Synchronizer(T1/E1 系統(tǒng)同步裝置(由一個數(shù)字鎖相環(huán)組成)) |

| MT9041A | () |

| MT9041B | T1/E1 System Synchronizer(T1/E1系統(tǒng)同步裝置(由一個數(shù)字鎖相環(huán)組成)) |

| MT9042B | () |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90221AL | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Quad IMA/UNI PHY Device |

| MT90222 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:4/8/16 Port IMA/TC PHY Device |

| MT90222AG | 制造商:Microsemi Corporation 功能描述:ATM IMA 40MBPS 2.5V 384BGA - Trays |

| MT90222AG2 | 制造商:Microsemi Corporation 功能描述:ATM IMA 40MBPS 2.5V 384BGA /BAKE/DRYPACK - Trays |

| MT90223AG | 制造商:Microsemi Corporation 功能描述:ATM IMA 80MBPS 2.5V 384BGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。