- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT90221 (Mitel Networks Corporation) Quad IMA/UNI PHY Device(四端口 IMA/UNI 物理層設(shè)備(四端口ATM IMA和UNI處理器)) PDF資料下載

參數(shù)資料

| 型號(hào): | MT90221 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Quad IMA/UNI PHY Device(四端口 IMA/UNI 物理層設(shè)備(四端口ATM IMA和UNI處理器)) |

| 中文描述: | 四IMA的/單向物理層設(shè)備(IMA的四端口/單向物理層設(shè)備(四端口自動(dòng)柜員機(jī)IMA的和單向處理器)) |

| 文件頁(yè)數(shù): | 21/116頁(yè) |

| 文件大?。?/td> | 309K |

| 代理商: | MT90221 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)

MT90221

13

location is transmitted in all ICP cells, Stuff

Cells and Filler cells sent on all the links that

are part of the corresponding TX IMA group

Byte 7 - the

TX Link ID

register is used to set

the Link Logical ID and the cell type is

determined by the internal controller on a per

link basis

Byte 8 - the frame sequence number is

controlled by an internal counter

Byte 9 - the

TX ICP Cell Offset

register is used

to set the value. This value is inserted on a per

link basis

Byte 10 - the link Stuff indication is inserted

automatically and the advance indication option

is programmed by the

TX IMA Control

register

on a per link basis

Byte 11 - the SCCI is controlled by internal

circuitry. The SCCI is incremented by one for

each transfer of the TX ICP cell from the buffer

area to the TX Cell RAM.

Byte 13 - the value of M is programmed through

the

TX Group Control Mode

register

Byte 14 - the

TX Group Control Mode

register

is used to set the Transmit Timing Information

and define the reference link

Bytes 52 and 53 - the calculated CRC-10 Error

Control bits are inserted automatically

Software controls all remaining bytes of the ICP

cells. It also maintains and updates all bytes that are

not directly controlled by the MT90221. A dedicated

address is reserved for each ICP cell byte for each of

the four IMA Groups. This permits direct access to

any of the bytes stored in each of the four

ICP Cell

registers. Refer to Table 2, ICP Cell Description, for

details on the ICP cell byte contents.

To avoid updating or corruption problems, the

internal copy of the ICP Cell cannot be directly

accessed. ICP cells are prepared in a buffer area

(RAM inside the MT90221) and transfer commands

are issued to copy the content of the ICP cell into the

internal Cell RAM area and to start using this new

ICP cell. The MT90221 uses a flag (status bit) to

indicate that this transfer is underway. Changes

should not be made to the content of the ICP cell in

the buffer area until the transfer to the internal

memory is complete. The status bit is cleared during

the transfer and returns to ’1’ on completion of the

transfer. IMA Groups are controlled independently.

When access to the ICP cell of one group is

prohibited, the other ICP cell buffer areas can still be

updated. The

TX ICP Cell Handler

and

TX ICP

Interrupt Enable

registers are used to initiate a

transfer and enable an optional interrupt to indicate

when the process is complete.

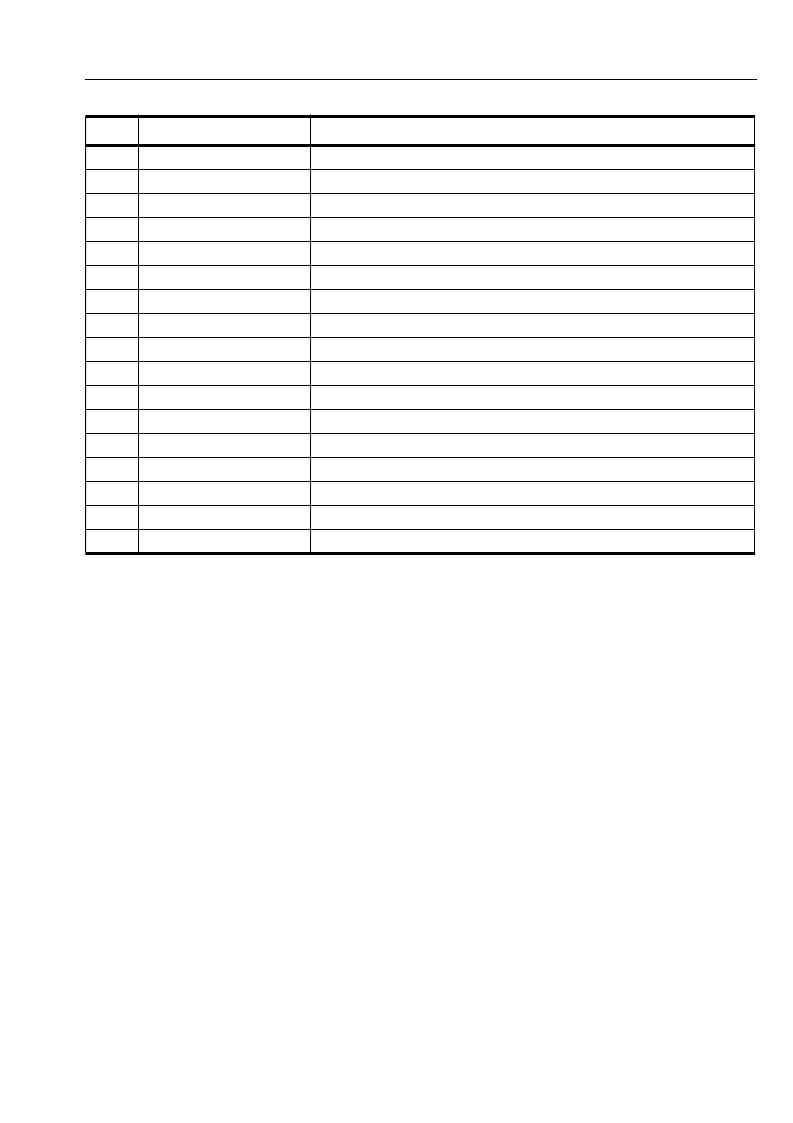

Table 2 - ICP Cell Description

Byte

Description

Control Source

1-5

ICP Cell Header

Content of Header is under S/W control. The HEC is calculated by H/W.

6

OAM label

S/W control

7

Cell ID, Link ID

The Link ID is programmed through other registers and inserted by H/W

8

IMA Frame Sequence

Hardware Control

9

ICP Cell Offset

H/W Control. (Programmed by S/W through other registers)

10

Link Stuff Indication

H/W Control

11

Status Change Indic.

H/W Control

12

IMA ID

S/W Control

13

Group Status and Control

S/W Control except for value of M

14

Sync. Info.

H/W Control (Programmed by S/W through other registers)

15

Test Control

S/W Control

16

TX Test Pattern

S/W Control

17

RX Test Pattern

S/W Control

18-49

Link Status and Control

S/W Control

50

Unused

S/W Control

51

End-to-End Channel

S/W Control

52-53

CRC Error Control

H/W Calculation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90401 | SONET/SDH System Synchronizer(SONET/SDH 系統(tǒng)同步裝置(由一個(gè)數(shù)字鎖相環(huán)組成)) |

| MT9040 | T1/E1 Synchronizer(T1/E1 系統(tǒng)同步裝置(由一個(gè)數(shù)字鎖相環(huán)組成)) |

| MT9041A | () |

| MT9041B | T1/E1 System Synchronizer(T1/E1系統(tǒng)同步裝置(由一個(gè)數(shù)字鎖相環(huán)組成)) |

| MT9042B | () |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90221AL | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Quad IMA/UNI PHY Device |

| MT90222 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:4/8/16 Port IMA/TC PHY Device |

| MT90222AG | 制造商:Microsemi Corporation 功能描述:ATM IMA 40MBPS 2.5V 384BGA - Trays |

| MT90222AG2 | 制造商:Microsemi Corporation 功能描述:ATM IMA 40MBPS 2.5V 384BGA /BAKE/DRYPACK - Trays |

| MT90223AG | 制造商:Microsemi Corporation 功能描述:ATM IMA 80MBPS 2.5V 384BGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。