- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377885 > MB814405C-60 (Fujitsu Limited) CMOS 1M ×4 BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×4 位超級頁面存取模式動態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號: | MB814405C-60 |

| 廠商: | Fujitsu Limited |

| 英文描述: | CMOS 1M ×4 BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×4 位超級頁面存取模式動態(tài)RAM) |

| 中文描述: | 的CMOS 100萬× 4位超頁模式動態(tài)RAM的CMOS(100萬× 4位超級頁面存取模式動態(tài)內(nèi)存) |

| 文件頁數(shù): | 13/30頁 |

| 文件大小: | 372K |

| 代理商: | MB814405C-60 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

13

MB814405C-60/MB814405C-70

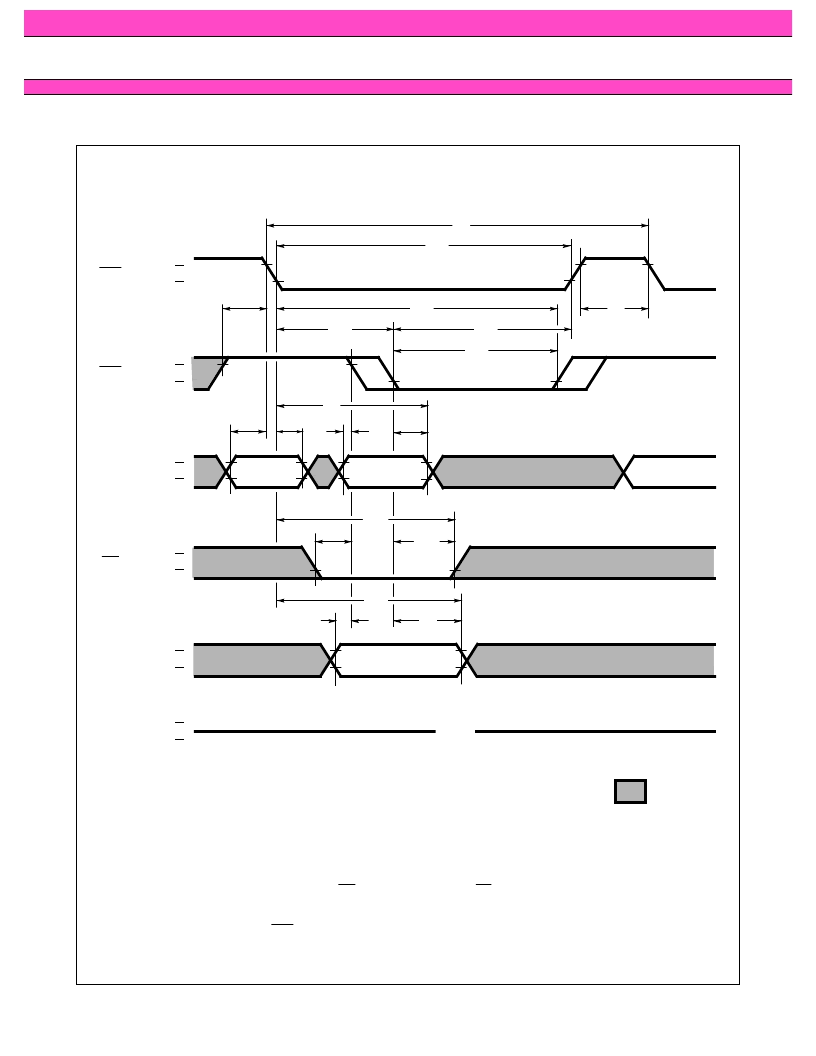

Fig. 6 – EARLY WRITE CYCLE

RAS

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

CAS

WE

DQ

(Input)

A

0

to A

9

V

OH

V

OL

DQ

(Output)

DESCRIPTION

A write cycle is similar to a read cycle except WE is set to a Low state and OE is a “H” or “L” signal. A write cycle can be

implemented in either of three ways–early write, delayed write, or read-modify-write. During all write cycles, timing param-

eters t

RWL

, t

CWL

, t

RAL

and t

CAL

must be satisfied. In the early write cycle shown above t

WCS

satisfied, data on the DQ pins are

latched with the falling edge of CAS and written into memory.

“H” or ”L”

t

RC

t

RAS

t

RP

t

CSH

t

RCD

t

CRP

t

CAS

t

ASR

t

RAH

t

ASC

t

CAH

HIGH-Z

ROW ADD

COLUMN ADD

t

WCR

t

WCS

t

WCH

t

DH

t

DS

VALID DATA IN

t

RSH

t

AR

t

DHR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB814405C-70 | CMOS 1M ×4 BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×4 位超級頁面存取模式動態(tài)RAM) |

| MB814405D-60 | 1M ×4BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×4 位超級頁面存取模式動態(tài)RAM) |

| MB814405D-60L | 1M ×4BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×4 位超級頁面存取模式動態(tài)RAM) |

| MB814405D-70 | 1M ×4BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×4 位超級頁面存取模式動態(tài)RAM) |

| MB814405D-7OL | 1M ×4BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×4 位超級頁面存取模式動態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB814405D-60PJN | 制造商:FUJITSU Component Ltd 功能描述: |

| MB8146112 | 制造商:FUJITSU 功能描述:* |

| MB81461-12PSZ | 制造商:FUJITSU 功能描述:VRAM, FAST PAGE, 64KX4, 24 Pin, Plastic, ZIP |

| MB81461B-12 | 制造商:FUJITSU 功能描述: 制造商:FUGITSU 功能描述:81461B-12 制造商:FUJITSU 功能描述:81461B-12 |

| MB81464-12 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:MOS 262,144 BIT DYNAMIC RANDOM ACCESS MEMORY |

發(fā)布緊急采購,3分鐘左右您將得到回復。