- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370961 > M44C090-H (ATMEL CORP) Low-Current Microcontroller for Wireless Communication PDF資料下載

參數(shù)資料

| 型號(hào): | M44C090-H |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Low-Current Microcontroller for Wireless Communication |

| 中文描述: | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| 封裝: | SSO-20 |

| 文件頁(yè)數(shù): | 15/63頁(yè) |

| 文件大小: | 503K |

| 代理商: | M44C090-H |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)

M44C890

M44C090

Rev.A4, 14-Dec-01

15 (63)

2.5

2.5.1

Clock Generation

Clock Module

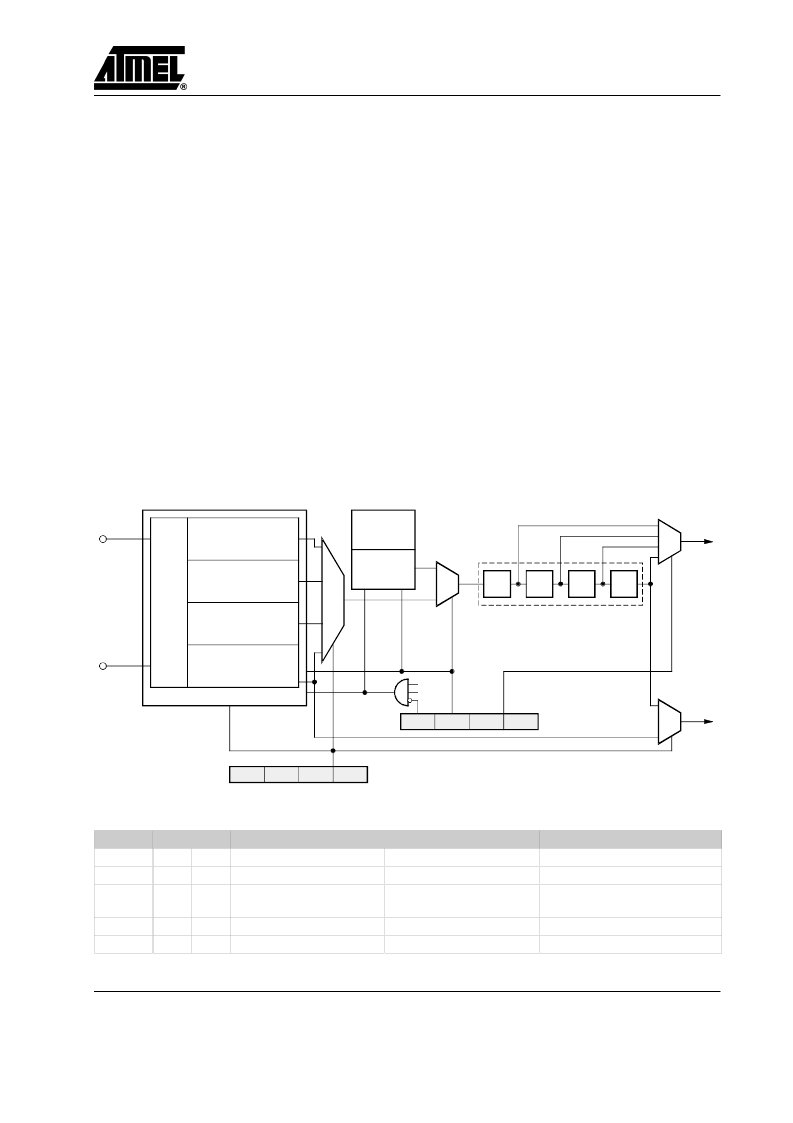

The M44C090 / M44C890 contains a clock module with

4 different internal oscillator types: two RC-oscillators,

one 4-MHz crystal oscillator and one 32-kHz crystal

oscillator. The pins OSC1 and OSC2 are the interface to

connect a crystal either to the 4-MHz, or to the 32-kHz

crystal oscillator. OSC1 can be used as input for external

clocks or to connect an external trimming resistor for the

RC-oscillator 2. All necessary circuitry except the crystal

and the trimming resistor is integrated on-chip. One of

these oscillator types or an external input clock can be

selected to generate the system clock (SYSCL).

In applications that do not require exact timing, it is

possible to use the fully integrated RC-oscillator 1

without any external components. The RC-oscillator 1

center frequency tolerance is better than

±

50%. The

RC-oscillator 2 is a trimmable oscillator whereby the

oscillator frequency can be trimmed with an external

resistor attached between OSC1 and V

DD

. In this

configuration, the RC-oscillator 2 frequency can be

maintained stable to within a tolerance of

±

15% over the

full operating temperature and voltage range.

The clock module is programmable via software with the

clock management register (CM) and the system

configuration register (SC). The required oscillator

configuration can be selected with the OS1-bit and the

OS0-bit in the SC-register. A programmable 4-bit divider

stage allows the adjustment of the system clock speed. A

special feature of the clock management is that an

external oscillator may be used and switched on and off

via a port pin for the power-down mode. Before the

external clock is switched off, the internal RC-oscillator

1 must be selected with the CCS-bit and then the SLEEP

mode may be activated. In this state an interrupt can wake

up the controller with the RC-oscillator, and the external

oscillator can be activated and selected by software. A

synchronization stage avoids too short clock periods if the

clock source or the clock speed is changed. If an external

input clock is selected, a supervisor circuit monitors the

external input and generates a hardware reset if the

external clock source fails or drops below 500 kHz for

more than 1 msec.

Ext. clock

ExIn

ExOut

Stop

RC oscillator2

RCOut2

Stop

R

Trim

4

–

MHz oscillator

Oscin

Oscout

4Out

Stop

Oscin

Oscout

32

–

kHz oscillator

Oscin

Oscout

32Out

RC

oscillator 1

RCOut1

Control

Stop

IN1

IN2

Cin

/2

/2

/2

/2

Divider

Sleep

WDL

Osc

–

Stop

NSTOP

CCS

CSS1

CSS0

CM:

BOT

–

–

–

OS1

OS0

SUBCL

SYSCL

SC:

OSC1

OSC2

Cin/16

32 kHz

Figure 14. Clock module

Table 5 Clock modes

Mode

Clock Source for SYSCL

CCS = 1

Clock Source for SUBCL

OS1

0

OS0

1

CCS = 0

áááááááááááááááááááááááááááááááá

áááááááááááááááááááááááááááááááá

áááááááááááááááááááááááááááááááá

2

RC-oscillator 2 with

external trimming resistor

C

/ 16

áááááááááááááááááááááááááááááááá

in

áááááááááááááááááááááááááááááááá

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M44C890 | Low-Current Microcontroller for Wireless Communication |

| M44C890-H | Low-Current Microcontroller for Wireless Communication |

| M4N25 | 6-Pin DIP Optoisolators Transistor Output |

| M4N26 | 6-Pin DIP Optoisolators Transistor Output |

| M4N37 | Header, Vertical Friction Lock; No. of Contacts:3; Pitch Spacing:2.54mm; No. of Rows:1; Gender:Header; Series:6410; Body Material:PA Polyamide (Nylon); Current Rating:4A; Voltage Rating:250V RoHS Compliant: Yes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M44C890 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44C890-H | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44S05K4F1 | 功能描述:汽車連接器 MX44 Terminals RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風(fēng)格: 端接類型: 觸點(diǎn)電鍍:Nickel |

| M44T332538880MHZ | 制造商:MEC 功能描述: |

| M44T3338880MHZ | 制造商:MEC 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。