- 您現在的位置:買賣IC網 > PDF目錄98007 > M38C59MF-XXXHP 8-BIT, MROM, 6.25 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數資料

| 型號: | M38C59MF-XXXHP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 6.25 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 12 X 12 MM, 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件頁數: | 16/75頁 |

| 文件大小: | 995K |

| 代理商: | M38C59MF-XXXHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁

Rev.2.00

Nov 23, 2005

page 23 of 73

REJ03B0028-0200

38C5 Group

b7

b0

Interrupt edge selection register

INT0 interrupt edge selection bit

INT1 interrupt edge selection bit

INT2 interrupt edge selection bit

Timer Y/CNTR1 interrupt switch bit

0 : Timer Y interrupt

1 : CNTR1 interrupt

INT0 input port switch bit

0 : Input from Port P62 (INT00)

1 : Input from Port P70 (INT01)

INT1 input port switch bit

0 : Input from Port P66 (INT10)

1 : Input from Port P71 (INT11)

Not used (return “0” when read)

(INTEDGE : address 003A16)

Interrupt request register 1

INT0 interrupt request bit

INT1 interrupt request bit

INT2 interrupt request bit

Key input interrupt request bit

Timer X interrupt request bit

Timer 1 interrupt request bit

Timer 2 interrupt request bit

Timer 3 interrupt request bit

Interrupt control register 1

INT0 interrupt enable bit

INT1 interrupt enable bit

INT2 interrupt enable bit

Key input interrupt enable bit

Timer X interrupt enable bit

Timer 1 interrupt enable bit

Timer 2 interrupt enable bit

Timer 3 interrupt enable bit

0 : No interrupt request issued

1 : Interrupt request issued

(IREQ1 : address 003C16)

(ICON1 : address 003E16)

Interrupt request register 2

Timer 4 interrupt request bit

Serial I/O1 receive interrupt request bit

Serial I/O1 transmit interrupt request bit

Serial I/O2 receive/transmit interrupt request bit

CNTR0 interrupt request bit

Timer Y interrupt request bit

CNTR1 interrupt request bit

AD conversion interrupt request bit

Not used (returns “0” when read)

(IREQ2 : address 003D16)

Interrupt control register 2

Timer 4 interrupt enable bit

Serial I/O1 receive interrupt enable bit

Serial I/O1 transmit interrupt enable bit

Serial I/O2 receive/transmit interrupt enable bit

CNTR0 interrupt enable bit

Timer Y interrupt enable bit

CNTR1 interrupt enable bit

AD conversion interrupt enable bit

Not used (returns “0” when read)

(Do not write to “1”.)

0 : Interrupts disabled

1 : Interrupts enabled

(ICON2 : address 003F16)

0 : Falling edge active

1 : Rising edge active

b7

b0

b7

b0

b7

b0

b7

b0

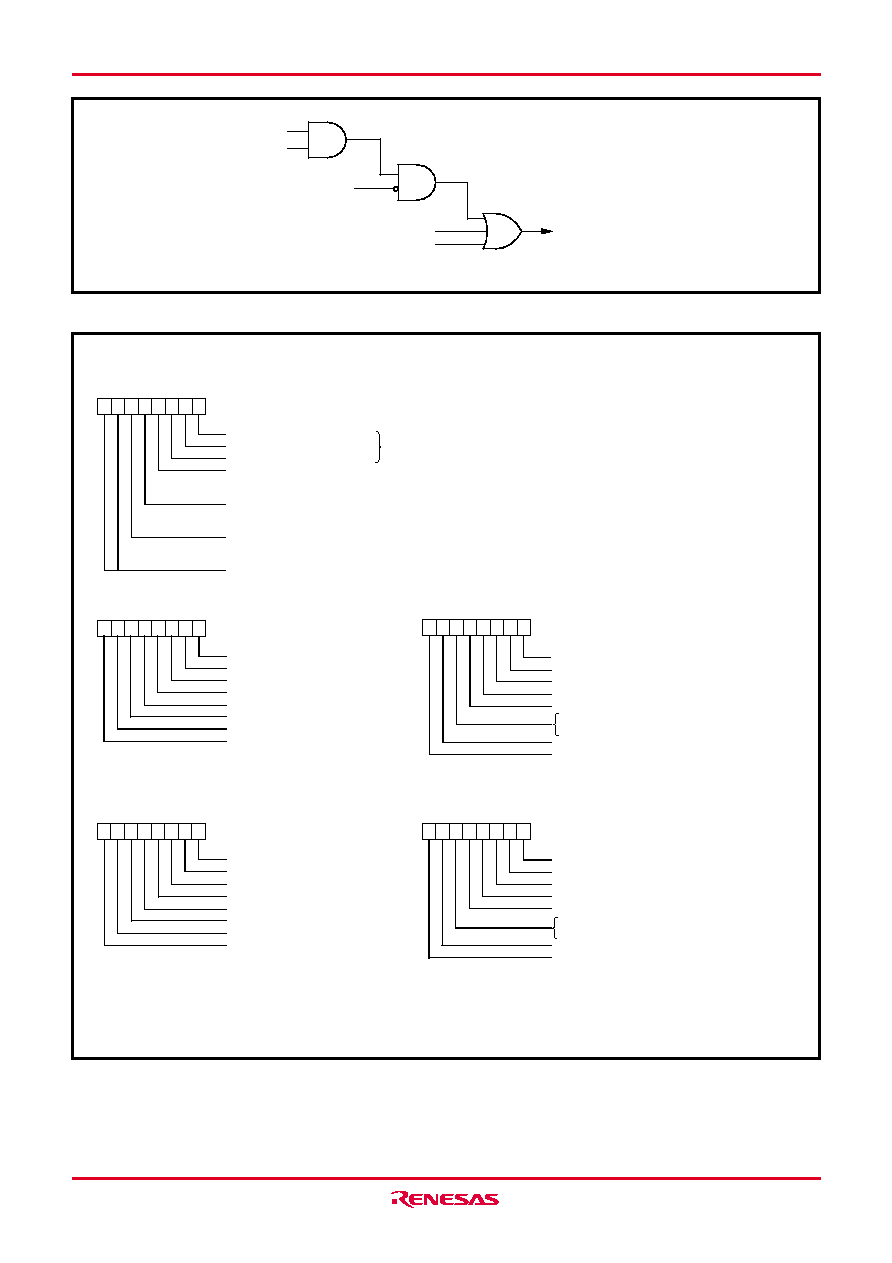

Fig. 18 Interrupt control

Fig. 19 Structure of interrupt-related registers

Interrupt request bit

Interrupt enable bit

Interrupt disable flag (I)

BRK instruction

Reset

Interrupt request

相關PDF資料 |

PDF描述 |

|---|---|

| M38K27M4-XXXHP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| M41ST87WMX6T | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M41T00SC64MY6E | REAL TIME CLOCK, PDSO18 |

| M41T00SM6F | 0 TIMER(S), REAL TIME CLOCK, PDSO8 |

| M41T00SMY6T | REAL TIME CLOCK, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M38D20F1XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D20F1XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D20F2XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D20F2XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D20F3XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復。