- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369872 > LU3X34FTR-HS128-DB Quad 3 V 10/100 Ethernet Transceiver TX/FX PDF資料下載

參數(shù)資料

| 型號: | LU3X34FTR-HS128-DB |

| 英文描述: | Quad 3 V 10/100 Ethernet Transceiver TX/FX |

| 中文描述: | 四3伏10/100以太網(wǎng)收發(fā)器德克薩斯州/外匯 |

| 文件頁數(shù): | 11/52頁 |

| 文件大?。?/td> | 678K |

| 代理商: | LU3X34FTR-HS128-DB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Lucent Technologies Inc.

11

Preliminary Data Sheet

July 2000

LU3X34FTR

Quad 3 V 10/100 Ethernet Transceiver TX/FX

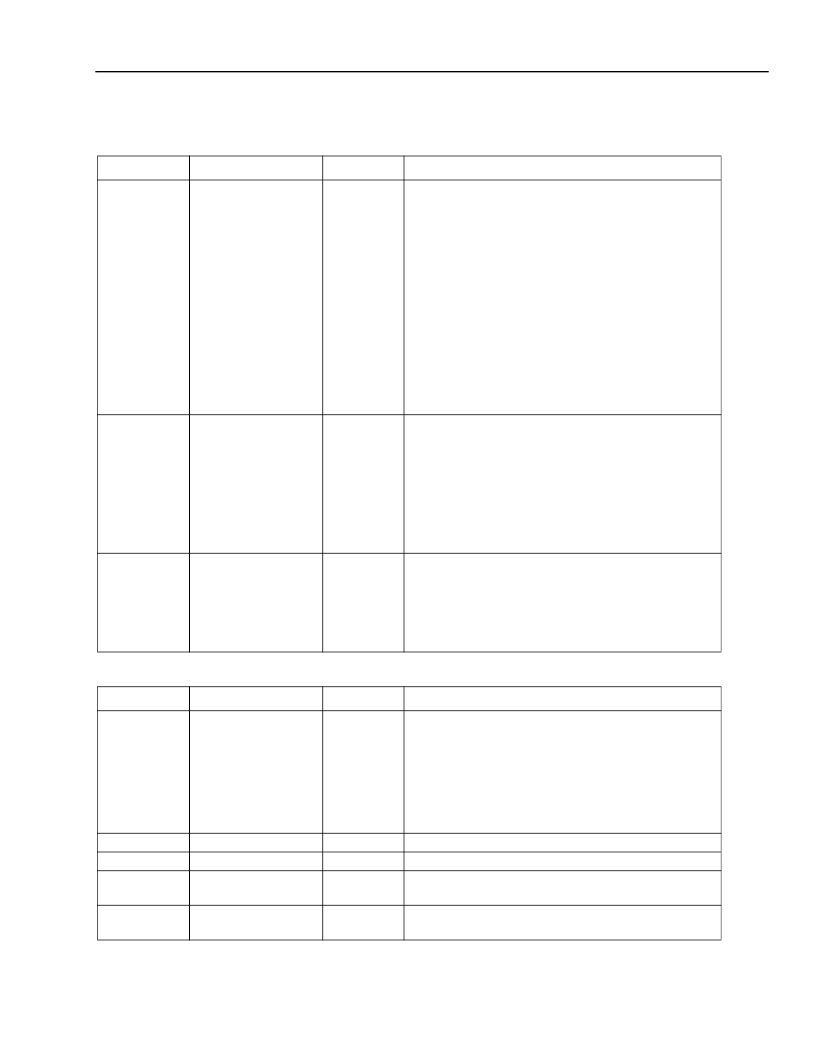

Table 7. Special Mode Configurations

* Smaller font indicates that the pin has multiple functions.

116, 122, 44,

50

LEDFD_[0:3]/

HD10_[0:3]/

SD–[0:3]

I/O

↑

Full-Duplex LED

Output

. Indicates full duplex for

ports 0—3.

10 Mbits/s Half-Duplex Operation

. If FOSEL is low

during powerup or reset, these are input pins that

configure ports 0—3 for 10 Mbits/s half-duplex oper-

ation and sets register 4, bit 5 (see Figure 12). When

autonegotiation is disabled, it sets register 0, bit 13,

the speed bit, to 0 and bit 8, the duplex mode bit, to

0. If fiber mode is selected, bit 5, register 4h will be

set to 0.

Signal Detect –

. In fiber mode, these pins are the

negative signal detect input from the fiber module.

These pins have an internal 40 k

pull-up resistor.

Activity LED Outputs

. These pins indicate collision

status of ports 0—3, respectively.

117, 123, 45,

51

LEDCOL_ [0:3]/

HD100_[0:3]

I/O

↑

100 Mbit/s Half-Duplex Operation.

During powerup

or reset, these are input pins to configure ports 0—3

for 100 Mbits/s half-duplex operation and sets regis-

ter 4, bit 7 (see Figure 12). If autonegotiation is dis-

abled, it sets bit 13 in register 0 to 1. These pins

have an internal 40 k

pull-up resistor.

Pause

. The logic level of this pin is latched into reg-

ister 4, bit 10 for all four ports during powerup or

reset. It is used to inform the autonegotiation link

partner that the MAC sublayer has pause/flow con-

trol capability when set in full-duplex mode. This

must not be set to 1 unless FD is also set.

40

PAUSE

I

Pin No.

118, 124, 46,

52

Pin Name*

LEDLNK_ [0:3]/

FOSEL _[0:3]

I/O

I/O

↓

Pin Description

Link LED Output

. Each of these LEDs turns on

when there is a good link and blinks when there is

activity.

Fiber-Optic Select

. These are input pins during

powerup and reset to configure ports 0—3 into fiber-

optic mode (see Figure 12). These pins have an

internal 40 k

pull-down resistor.

Interrupt

. Open drain only pin.

Test Mode Select.

This pin should be tied low.

Isolate.

If this pin is high, all MII inputs are ignored

and all MII outputs are 3-stated.

Reserved

. These are a reserved pins and should be

left floating.

39

125

42

INTZ

O

I

I

TESTMSEL

ISOLATE

128, 87, 70,

65

RESERVED

—

Pin No.

Pin Name

I/O

Pin Description

Pin Descriptions

(continued)

Table 6. LED/Configuration Pins

(continued)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LU3X34FTR | Quad 3 V 10/100 Ethernet Transceiver(四通道10M位/秒和100 M位/秒以太網(wǎng)收發(fā)器) |

| LU3X54FT | QUAD-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX |

| LU3X54FTL | QUAD-FET for 10Base-T/100Base-TX/FX |

| LU3X54FTL-HS208-DB | QUAD-FET for 10Base-T/100Base-TX/FX |

| LU3X54FT | Quad-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX(應(yīng)用于10基數(shù)-T和100基數(shù)-TX/FX的四快速以太網(wǎng)收發(fā)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LU3X54FT | 制造商:AGERE 制造商全稱:AGERE 功能描述:QUAD-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX |

| LU3X54FTL | 制造商:AGERE 制造商全稱:AGERE 功能描述:QUAD-FET for 10Base-T/100Base-TX/FX |

| LU3X54FTLHS208 | 制造商:Alcatel-Lucent 功能描述:3X54FTLHS208 |

| LU3X54FTL-HS208-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:QUAD-FET for 10Base-T/100Base-TX/FX |

| LU3X54FTLHS208-DB | 制造商:Alcatel-Lucent 功能描述:3X54FTLHS208-DB |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。