- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370783 > HYB25D128400AT (INFINEON TECHNOLOGIES AG) 128 Mbit Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號: | HYB25D128400AT |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 128 Mbit Double Data Rate SDRAM |

| 中文描述: | 128兆雙倍數(shù)據(jù)速率SDRAM |

| 文件頁數(shù): | 26/79頁 |

| 文件大?。?/td> | 2596K |

| 代理商: | HYB25D128400AT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁

CL=2.5

HYB25D128[400/800/160]A-[6/7/8]

128Mbit Double Data Rate SDRAM

Functional Description

Data Sheet

26

Rev. 1.06, 2004-01

09192003-LFQ1-R60G

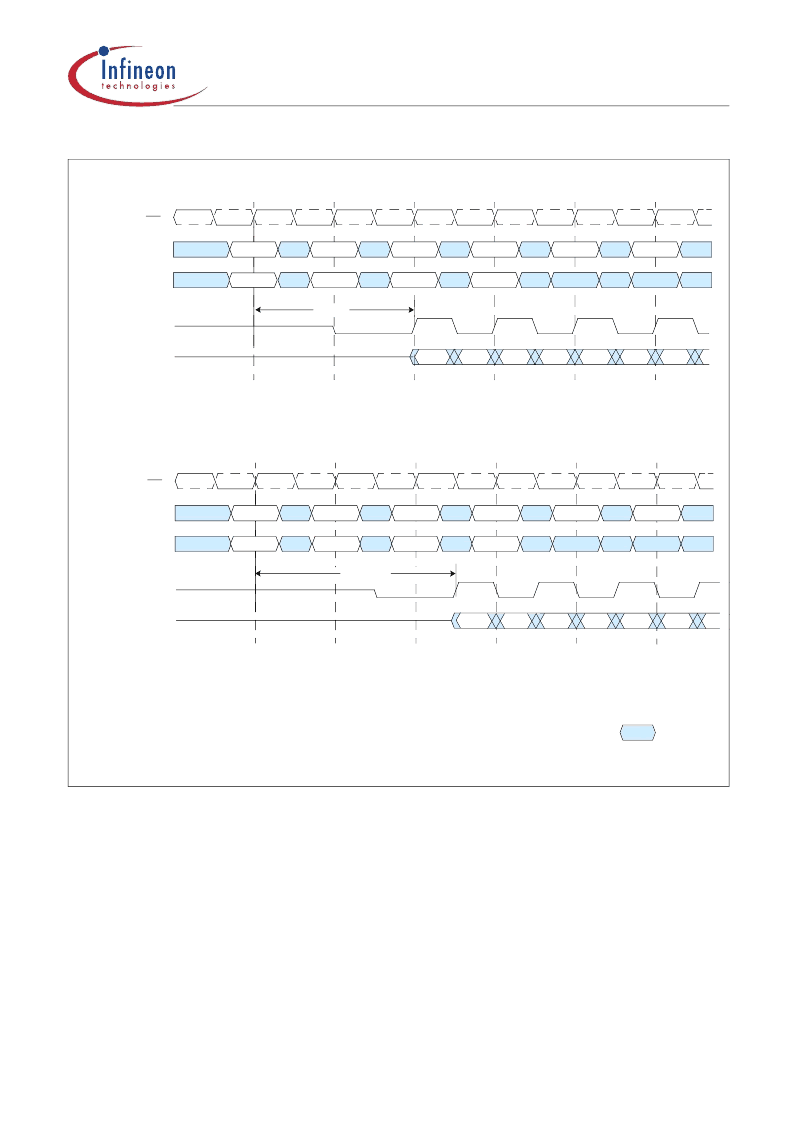

Figure 12

Random Read Accesses: CAS Latencies (Burst Length = 2, 4 or 8)

Data from any Read burst may be truncated with a Burst Terminate command, as shown on

Figure 9 "Read

Burst: CAS Latencies (Burst Length = 4)" on Page 23

. The Burst Terminate latency is equal to the read (CAS)

latency, i.e. the Burst Terminate command should be issued

×

cycles after the Read command, where

×

equals

the number of desired data element pairs.

Data from any Read burst must be completed or truncated before a subsequent Write command can be issued. If

truncation is necessary, the Burst Terminate command must be used, as shown on

Figure 14 "Read to Write:

CAS Latencies (Burst Length = 4 or 8)" on Page 28

. The example is shown for

t

DQSS

(min). The

t

DQSS

(max)

case, not shown here, has a longer bus idle time.

t

DQSS

(min) and

t

DQSS

(max) are defined in the section on Writes.

A Read burst may be followed by, or truncated with, a Precharge command to the same bank (provided that Auto

Precharge was not activated). The Precharge command should be issued

×

cycles after the Read command,

where

×

equals the number of desired data element pairs (pairs are required by the 2n prefetch architecture). This

is shown on

Figure 15 "Read to Precharge: CAS Latencies (Burst Length = 4 or 8)" on Page 29

for Read

latencies of 2 and 2.5. Following the Precharge command, a subsequent command to the same bank cannot be

DOa-n

CAS Latency = 2

Read

Read

Read

NOP

NOP

Read

DOa-b

DOa-n'

DOa-x

DOa-x'

DOa-b’

DOa-g

CK

CK

Command

Address

DQS

DQ

DO a-n, etc. = data out from bank a, column n etc.

n' etc. = odd or even complement of n, etc. (i.e., column address LSB inverted).

Reads are to active rows in any banks.

Shown with nominal t

AC

, t

DQSCK

, and t

DQSQ

.

Don’t Care

BAa, COL n

BAa, COL x

BAa, COL b

BAa, COL g

CL=2

DOa-n

CAS Latency = 2.5

Read

Read

Read

NOP

NOP

Read

DOa-b

DOa-n'

DOa-x

DOa-x'

DOa-b’

CK

CK

Command

Address

DQS

DQ

BAa, COL n

BAa, COL x

BAa, COL b

BAa, COL g

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB25D128400AT-6 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128400ATL-8 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128800AT-6 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128800ATL-8 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128400CC-6 | 128 Mbit Double Data Rate SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB25D128400AT-6 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit Double Data Rate SDRAM |

| HYB25D128400AT-7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:?128Mb (32Mx4) DDR266A (2-3-3)? |

| HYB25D128400AT-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:?128Mb (32Mx4) DDR200 (2-2-2)? |

| HYB25D128400ATL-6 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit Double Data Rate SDRAM |

| HYB25D128400ATL-7 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit Double Data Rate SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。