- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄97907 > ELANSC410 Single Synchronous Buck Pulse-Width Modulation (PWM) Controller; Temperature Range: 0°C to 70°C; Package: 16-QFN PDF資料下載

參數(shù)資料

| 型號(hào): | ELANSC410 |

| 英文描述: | Single Synchronous Buck Pulse-Width Modulation (PWM) Controller; Temperature Range: 0°C to 70°C; Package: 16-QFN |

| 中文描述: | ElanSC410 - ElanSC410框圖 |

| 文件頁(yè)數(shù): | 63/119頁(yè) |

| 文件大小: | 1167K |

| 代理商: | ELANSC410 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)當(dāng)前第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)

48

lanSC310 Microcontroller Data Sheet

PREL IMINARY

The lanSC300 microcontroller samples the two reset

inputs (RESIN and IORESET) to logically determine

what state the power pins are in; and, in turn, controls

the internal pull-down resistors. Note that in Micro

Power Off mode, the IORESET input should be termi-

nated with a pull-down resistor if not driven Low by an

external device (see Table 23 on page 50 for more in-

formation about internal I/O pull-down states).

Micro Power Off DRAM Refresh

Refresh can be either enabled or disabled during Micro

Power Off mode, and the VMEM power can be option-

ally removed, provided that either the memory is also

powered off or all DRAM interface signals are kept at

The system designer has the option to keep the system

DRAM powered up and refreshed while the lanSC310

microcontroller is in the micro power state. A configura-

tion bit, the Micro Power Refresh Enabled bit, exists in

the PMU section of the core logic to realize this feature.

This is bit 2 of the Miscellaneous 3 Register at Index

BAh. If this bit is cleared (default), the core logic asso-

ciated with the DRAM refresh will be disabled when the

lanSC310 microcontroller is in the Micro Power state.

If the bit is set, the core logic associated with the DRAM

refresh will be enabled and functional while the

lanSC310 microcontroller is in its Micro Power state.

The type of Micro Power DRAM refresh performed

(CAS-before-RAS refresh, or self refresh) will be the

same as that for which the part was configured before

the IORESET pin sampled Low. If the micro power re-

fresh feature is enabled for CAS-before-RAS refresh,

the system designer should maintain power on the

VMEM power pin of the lanSC310 microcontroller

and not remove power from the DRAM devices. If the

micro power refresh feature is enabled for self refresh,

the system designer may or may not be required to

maintain power on the VMEM power pin of the

lanSC310 microcontroller, depending on the specific

requirement of the DRAM device in Self-Refresh mode.

Power should not be removed from the DRAM device

itself in either case.

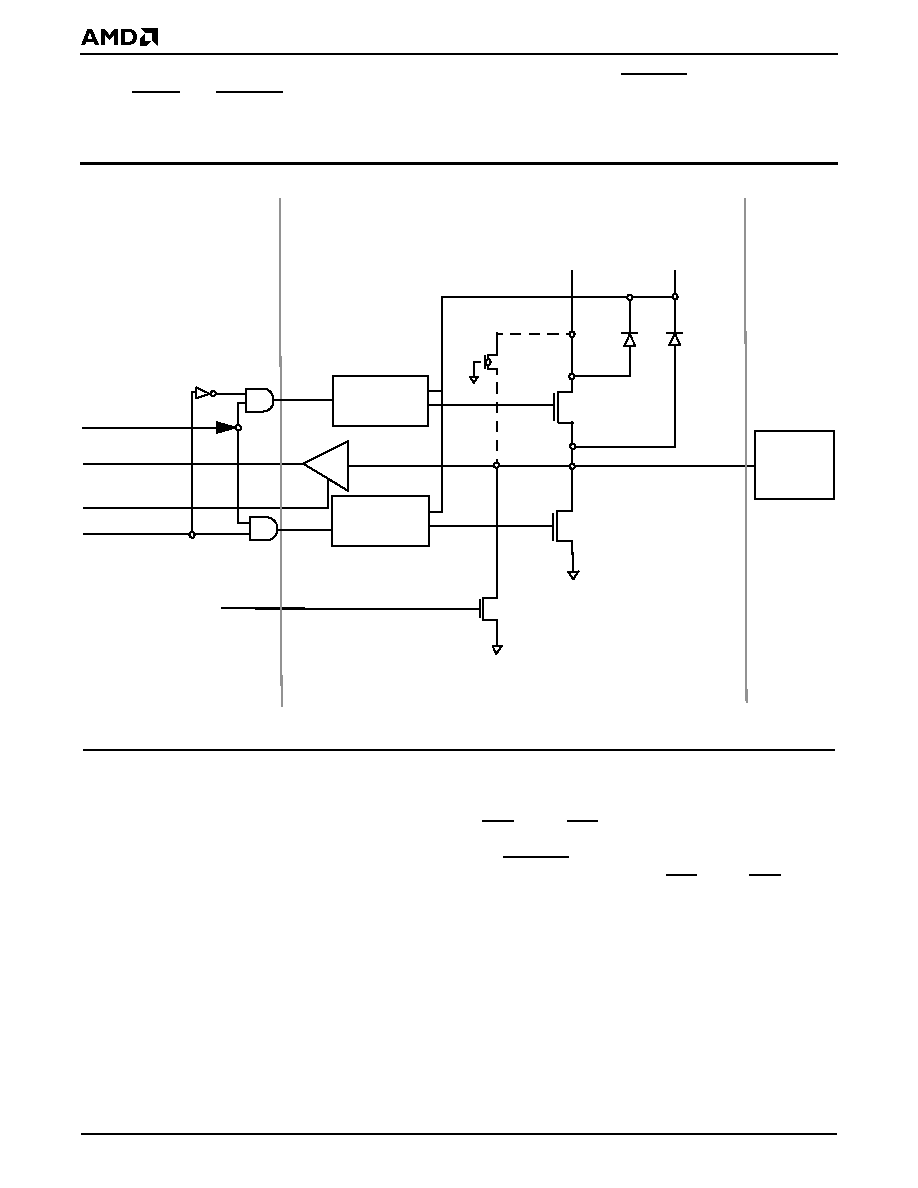

IN

BUF

Level

Translator and

Pre-Driver

Level

Translator and

Pre-Driver

I/O

PAD

Pull-Up

Resistor

VCCIO

VCC CLAMP

Core Logic

I/O Driver

Pins

To Core Logic

VCC Core

Force Term

Pull-Down

Resistor

Data Out

Output Enable

Where: VCCIO = VCC5, VMEM, VSYS, VSYS2, AVCC, or VCC1

VCC CLAMP = VCC5, VMEM, or AVCC

Figure 4.

lanSC310 Microcontroller I/O Structure

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ELH0032G | Fast Operational Amplifier |

| ELH0033G | Fast Buffer Amplifier |

| ELH0101CK | Dual Regulator-Standard Buck PWM and Linear Power Controller; Temperature Range: 0°C to 70°C; Package: 8-SOIC T&R |

| ELH0101ACK | Single Synchronous Buck Pulse-Width Modulation (PWM) Controller; Temperature Range: -40°C to 85°C; Package: 16-QFN |

| ELH0101 | Power Operational Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ELANSC410-100AC | 制造商:Advanced Micro Devices 功能描述:MCU 16-Bit/32-Bit Elan CISC ROMLess 3.3V 292-Pin BGA |

| ELANSC410-100ACAD | 制造商:Advanced Micro Devices 功能描述: |

| ELANSC410-100AI | 制造商:AMD 制造商全稱(chēng):Advanced Micro Devices 功能描述:Single-Chip, Low-Power, PC/AT-Compatible Microcontrollers |

| ELANSC410-33AC | 制造商:Advanced Micro Devices 功能描述:MCU 16-Bit/32-Bit Elan CISC 3.3V 292-Pin BGA |

| ELANSC410-33AI | 制造商:AMD 制造商全稱(chēng):Advanced Micro Devices 功能描述:Single-Chip, Low-Power, PC/AT-Compatible Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。