- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293971 > 5962-9205805QXA (TEXAS INSTRUMENTS INC) 32-BIT, 60 MHz, OTHER DSP, CPGA141 PDF資料下載

參數(shù)資料

| 型號: | 5962-9205805QXA |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 32-BIT, 60 MHz, OTHER DSP, CPGA141 |

| 封裝: | STAGGERED, CERAMIC, PGA-141 |

| 文件頁數(shù): | 30/54頁 |

| 文件大小: | 1033K |

| 代理商: | 5962-9205805QXA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

SMJ320C31, SMJ320LC31, SMQ320LC31

DIGITAL SIGNAL PROCESSORS

SGUS026G APRIL 1998 REVISED SEPTEMBER 2006

36

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

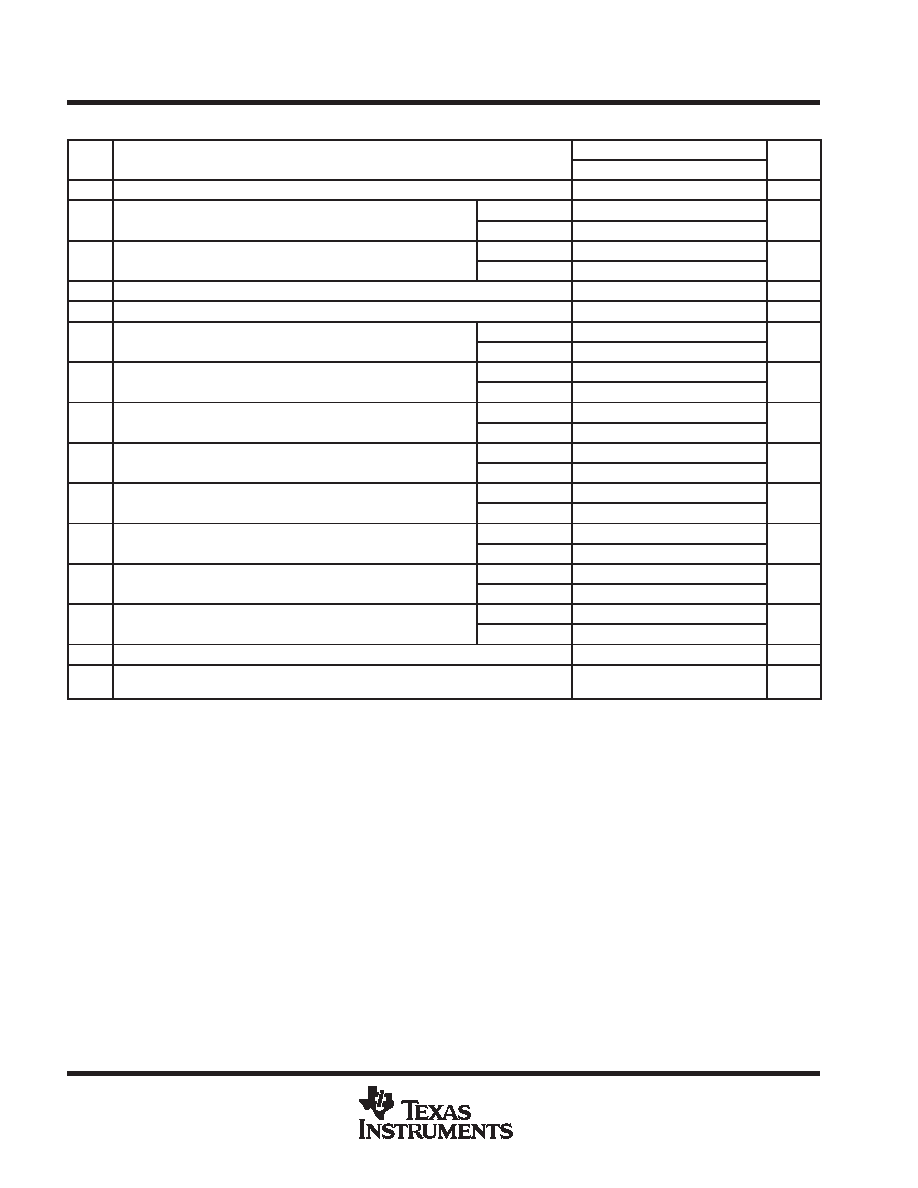

serial-port timing for SMJ320C31-60 (see Figure 26 and Figure 27)

NO.

’C31-60

UNIT

NO.

MIN

MAX

UNIT

54

td(H1H-SCK)

Delay time, H1 high to internal CLKX/R

8

ns

55

tc(SCK)

Cycle time, CLKX/R

CLKX/R ext

tc(H)x2.6

ns

55

tc(SCK)

Cycle time, CLKX/R

CLKX/R int

tc(H)x2

tc(H)x232

ns

56

tw(SCK)

Pulse duration, CLKX/R high/low

CLKX/R ext

tc(H)+10

ns

56

tw(SCK)

Pulse duration, CLKX/R high/low

CLKX/R int

[tc(SCK)/2]5

[tc(SCK)/2]+5

ns

57

tr(SCK)

Rise time, CLKX/R

5

ns

58

tf(SCK)

Fall time, CLKX/R

5

ns

59

td(C-DX)

Delay time, CLKX to DX valid

CLKX ext

20

ns

59

td(C-DX)

Delay time, CLKX to DX valid

CLKX int

15

ns

60

tsu(DR-CLKRL)

Setup time, DR before CLKR low

CLKR ext

8

ns

60

tsu(DR-CLKRL)

Setup time, DR before CLKR low

CLKR int

15

ns

61

th(CLKRL-DR)

Hold time, DR from CLKR low

CLKR ext

6

ns

61

th(CLKRL-DR)

Hold time, DR from CLKR low

CLKR int

0

ns

62

td(C-FSX)

Delay time, CLKX to internal FSX high/low

CLKX ext

20

ns

62

td(C-FSX)

Delay time, CLKX to internal FSX high/low

CLKX int

14

ns

63

tsu(FSR-CLKRL)

Setup time, FSR before CLKR low

CLKR ext

6

ns

63

tsu(FSR-CLKRL)

Setup time, FSR before CLKR low

CLKR int

6

ns

64

th(SCKL-FS)

Hold time, FSX/R input from CLKX/R low

CLKX/R ext

6

ns

64

th(SCKL-FS)

Hold time, FSX/R input from CLKX/R low

CLKX/R int

0

ns

65

tsu(FSX-C)

Setup time, external FSX before CLKX

CLKX ext

[tc(H) 8]*

[tc(SCK)/2] 10*

ns

65

tsu(FSX-C)

Setup time, external FSX before CLKX

CLKX int

[tc(H) 21]*

tc(SCK)/2*

ns

66

td(CH-DX)V

Delay time, CLKX to first DX bit, FSX

CLKX ext

20*

ns

66

td(CH-DX)V

Delay time, CLKX to first DX bit, FSX

precedes CLKX high

CLKX int

12*

ns

67

td(FSX-DX)V

Delay time, FSX to first DX bit, CLKX precedes FSX

20*

ns

68

td(CH-DXZ)

Delay time, CLKX high to DX high impedance following last

data bit

12*

ns

* This parameter is not production tested.

相關PDF資料 |

PDF描述 |

|---|---|

| 5962-9309101HYA | EEPROM 5V MODULE, CDIP32 |

| 5962-9315302MXX | 4K X 9 MULTI-PORT SRAM, 25 ns, CQCC |

| 596287663012X | ACT SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, CQCC20 |

| 5962D0053605QYX | 512K X 8 STANDARD SRAM, 20 ns, CDFP36 |

| 5962D1022901QXC | 64M X 40 SYNCHRONOUS DRAM, 5.4 ns, CQFP128 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-9205805QYA | 制造商:Texas Instruments 功能描述:DSP FLOATING PT 32BIT 60MHZ 30MIPS 132CFPAK - Rail/Tube |

| 596292062012MYC | 制造商:ALTERA 功能描述:EPM5192GM883B |

| 5962-92062012MYC | 制造商:ALTERA 功能描述:EPM5192GM883B |

| 5962-9206201MYC | 制造商:Cypress Semiconductor 功能描述:CPLD 192 Macro Cells 0.8um (CMOS) Technology 5V 84-Pin Windowed PGA |

| 5962-9206202MYC | 制造商:e2v Aerospace & Defense 功能描述:CPLD, UV ERASABLE, 192-MACROCELL, 30 NS PROP. DELAY TIME |

發(fā)布緊急采購,3分鐘左右您將得到回復。