- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156622 > 4565B2 (LSI CORP) ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 PDF資料下載

參數(shù)資料

| 型號: | 4565B2 |

| 廠商: | LSI CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 封裝: | PLASTIC, BGA-909 |

| 文件頁數(shù): | 43/61頁 |

| 文件大小: | 1691K |

| 代理商: | 4565B2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

4565B Ultramapper Full Transport Retiming Device

Hardware Design Guide, Revision 2

622/155 Mbits/s SONET/SDH x DS3/E3/DS2/DS1/E1

December 17, 2003

48

Agere Systems Inc.

6 Reference Clocks

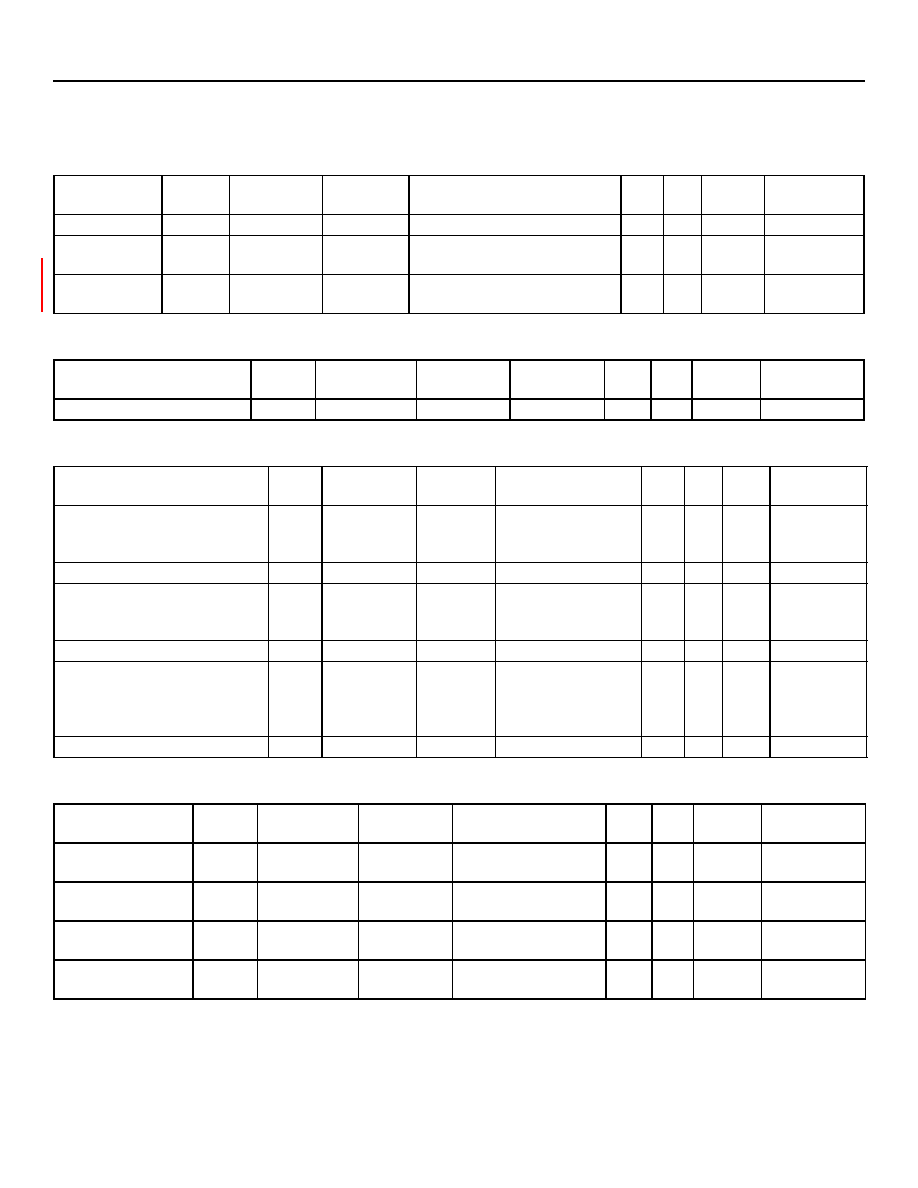

Table 6-1. High-Speed Interface Input Clocks Specifications

Clock Name

Period

(ns)

Frequency

Accuracy

(ppm)

Jitter

Rise

(ns)

Fall

(ns)

Min/

Max

Duty Cycle

RHSCP/N

6.43

155.52 MHz

20

—

0.4

0.4 nominal

50% ± 5%

THSCP/N

6.43

155.52 MHz

20

0.01 UIp-p or 64 psp-p or

0.001 UIrms (12 kHz—1.3 MHz)

0.4

0.4 nominal

50% ± 5%

THSCP/N

1.6

622.08 MHz

20

0.04 UIp-p or 64 psp-p

(12 kHz—5 MHz)

0.4

nom

0.6

max

—50% ± 5%

Table 6-2. Protection Link Input Clock Specifications

Clock Name

Period

(ns)

Frequency

Accuracy

(ppm)

Jitter

Rise

(ns)

Fall

(ns)

Min/Max

Duty Cycle

RPSCP/N

6.43

155.52 MHz

20

—

0.4

nominal

50% ± 5%

Table 6-3. DS3/E3/STS-1 Input Clocks Specifications

Clock Name

Period

(ns)

Frequency Accuracy

(ppm)

Jitter

Rise

(ns)

Fall

(ns)

Min/

Max

Duty Cycle

DS3DATAOUTCLK[6:1] (DS3) 22.353 44.736 MHz

20

0.05 UIp-p or

1.12 nsp-p

(10 kHz—400 kHz)

5

max

50% ± 10%

DS3DATAINCLK[6:1](DS3)

22.353 44.736 MHz

20

—

3.5

2.5

max

50% ± 5%

DS3DATAOUTCLK[6:1](E3)

29.090 34.368 MHz

20

0.03 UIp-p or

0.87 nsp-p

(100 kHz—800 kHz)

5

max

50% ± 10%

DS3DATAINCLK[6:1]](E3)

29.090 34.368 MHz

20

—

3.5

2.5

max

50% ± 5%

DS3DATAOUTCLK[6:1](STS-1) 19.290 51.84 MHz

20

0.01 UIp-p or

0.19 nsp-p or

0.001 UIrms

(12 kHz—400 kHz)

5

max

50% ± 10%

DS3DATAINCLK[6:1](STS-1)

19.290 51.84 MHz

20

—

3.5

2.5

max

50% ± 5%

Table 6-4. DS1/E1 DJA Input Clocks Specifications

Clock Name

Period

(ns)

Frequency

Accuracy

(ppm)

Jitter

Rise

(ns)

Fall

(ns)

Min/Max

Duty Cycle

E1XCLK

15.25

65.536 MHz

50

0.1 UIp-p or 1.5 nsp-p

(20 kHz—100 kHz)

3.5

Max

50% ± 10%

DS1XCLK

20.20

49.408 MHz

32

0.1 UIp-p or 2.0 nsp-p

(10 kHz—40 kHz)

3.5

Max

50% ± 10%

E1XCLK

30.52

32.768 MHz

50

0.1 UIp-p or 3.0 nsp-p

(20 kHz—100 kHz)

3.5

Max

50% ± 10%

DS1XCLK

40.40

24.704 MHz

32

0.1 UIp-p or 4.0 nsp-p

(10 kHz—40 kHz)

3.5

Max

50% ± 10%

相關PDF資料 |

PDF描述 |

|---|---|

| 4565B2 | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 45APC180K | 1 ELEMENT, 18 uH, GENERAL PURPOSE INDUCTOR |

| 45APC470K | 1 ELEMENT, 47 uH, GENERAL PURPOSE INDUCTOR |

| 45APC272K | 1 ELEMENT, 2700 uH, GENERAL PURPOSE INDUCTOR |

| 45K101-101H3 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 4565-BLK | 制造商:Pomona Electronics 功能描述:ACCESSORIES, MAXIGRABBER TEST CLIP |

| 4565-BLK-3XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標準包裝:1 |

| 4565-BLK-4XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標準包裝:1 |

| 4565-BLK-L | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標準包裝:1 |

| 4565-BLK-M | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標準包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復。