- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156622 > 4565B2 (LSI CORP) ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 PDF資料下載

參數(shù)資料

| 型號(hào): | 4565B2 |

| 廠商: | LSI CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 封裝: | PLASTIC, BGA-909 |

| 文件頁數(shù): | 40/61頁 |

| 文件大?。?/td> | 1691K |

| 代理商: | 4565B2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

Hardware Design Guide, Revision 2

4565B Ultramapper Full Transport Retiming Device

December 17, 2003

622/155 Mbits/s SONET/SDH x DS3/E3/DS2/DS1/E1

Agere Systems Inc.

45

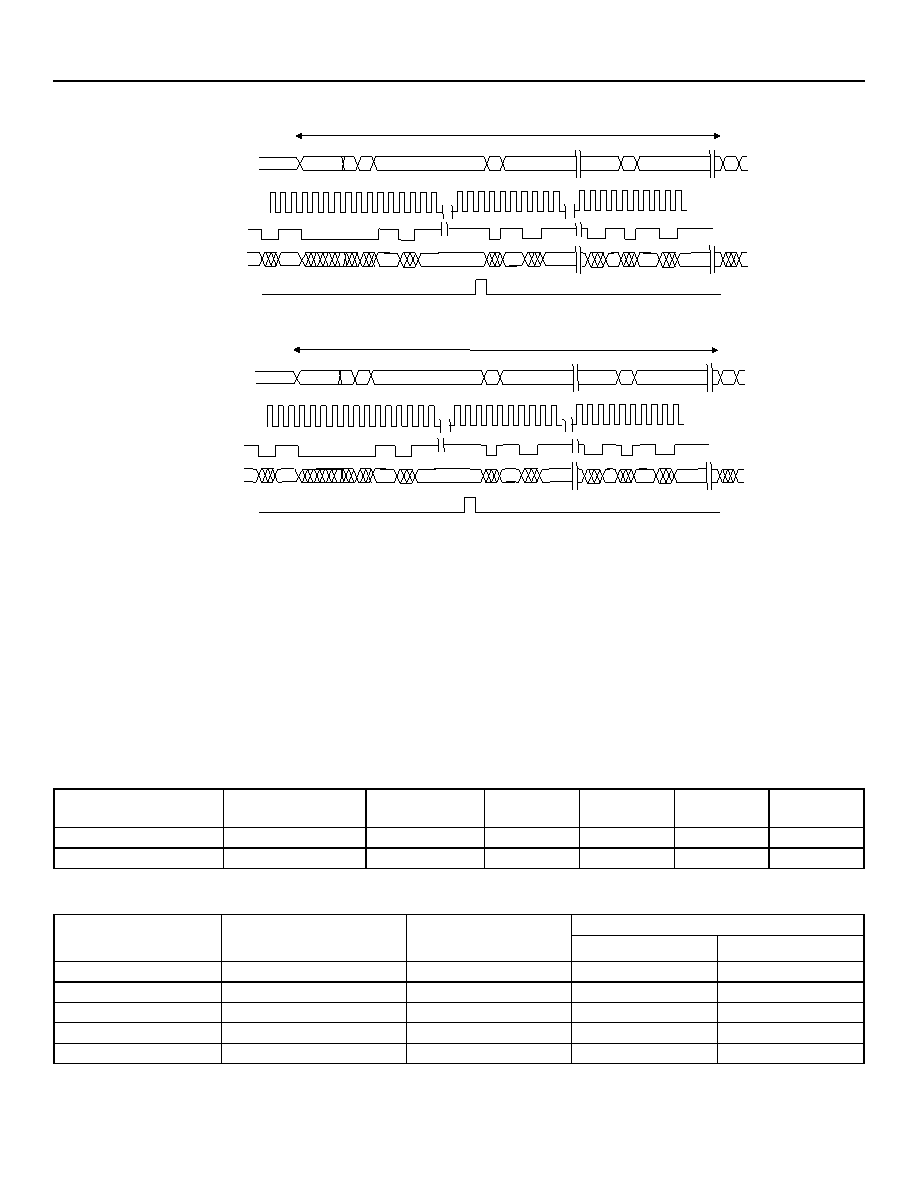

Figure 5-16. NSMI Clock and Data Diagram for E13 NSMI Mode 2 (NSMI <--> E13 <--> SPEMPR <--> STM-N)

Table 5-12. NSMI Inputs Specifications

Name

Reference

Edge

Rising/Falling

Max Rise

Time (ns)

Max Fall

Time (ns)

Min Setup

(ns)

Min Hold

(ns)

NSMIRXDATA[3:1]

NSMIRXCLK

R

3.5

5

0

NSMIRXSYNC[3:1]

NSMIRXCLK

R

3.5

5

0

Table 5-13. NSMI Outputs Specifications

Name

Reference

Edge

Rising/Falling

Propagation Delay

Min (ns)

Max (ns)

NSMITXDATA[3:1]

NSMITXCLK

R

0.5

8.75

NSMITXSYNC[3:1]

NSMITXCLK

R

0.5

8.75

RXDATAEN[3:1]

NSMIRXCLK

R

0.5

8.75

TXDATAEN[3:1]

NSMITXCLK

R

0.5

8.75

NSMIRXSYNC[3:1]

NSMIRXCLK

R

0.5

8.75

NSMI_TXDATAEN

(output)

NSMI_TXCLK

(51.84 MHz output)

E3 frame

(for info only)

NSMI_TXDATA

(output)

NSMI_TXSYNC

(output)

NSMI_RXCLK

(51.84 MHz output)

E3 frame

(For info only)

NSMI_RXDATA

(Input)

NSMI_RXSYNC

(output)

NSMI_RXDATAEN

(output)

1536 bits

Position of this pulse is provisionable 0-256 bits before C11

FRAME, RAI, RSVD

C11 = 0

Cj3 = 0

Frame

Stuff = data

1536 bits

Position of this pulse is provisionable 0-256 bits before C11

FRAME, RAI, RSVD

C11 = 0

Cj3 = 0

Frame

Stuff = data

Notes:

Clock from E13 is at 51.84 MHz rate and is not gapped. TXDATAEN is the combination of an internal clock enable and data enable from SPEMPR.

TXDATAEN is used to mark the overhead time and control bits time of the E3 frame. Clock enable is used to gap the clock rate to 34.368 MHz.

C11’s (the first C bit of the first tributary) position is optionally marked by TXSYNC, which is provisioned to be 0 to 255 bits before C11 (bit 385 of the E3

frame).

During periods where the OH is present, the TXDATAEN signal goes low.

All C bits are zero and the stuff bits are used for data.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 4565B2 | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 45APC180K | 1 ELEMENT, 18 uH, GENERAL PURPOSE INDUCTOR |

| 45APC470K | 1 ELEMENT, 47 uH, GENERAL PURPOSE INDUCTOR |

| 45APC272K | 1 ELEMENT, 2700 uH, GENERAL PURPOSE INDUCTOR |

| 45K101-101H3 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 4565-BLK | 制造商:Pomona Electronics 功能描述:ACCESSORIES, MAXIGRABBER TEST CLIP |

| 4565-BLK-3XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-4XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-L | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-M | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。