- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156622 > 4565B2 (LSI CORP) ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 PDF資料下載

參數(shù)資料

| 型號(hào): | 4565B2 |

| 廠商: | LSI CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 封裝: | PLASTIC, BGA-909 |

| 文件頁(yè)數(shù): | 31/61頁(yè) |

| 文件大小: | 1691K |

| 代理商: | 4565B2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

Hardware Design Guide, Revision 2

4565B Ultramapper Full Transport Retiming Device

December 17, 2003

622/155 Mbits/s SONET/SDH x DS3/E3/DS2/DS1/E1

Agere Systems Inc.

37

5 Timing

5.1 TMUX High-Speed Interface Timing

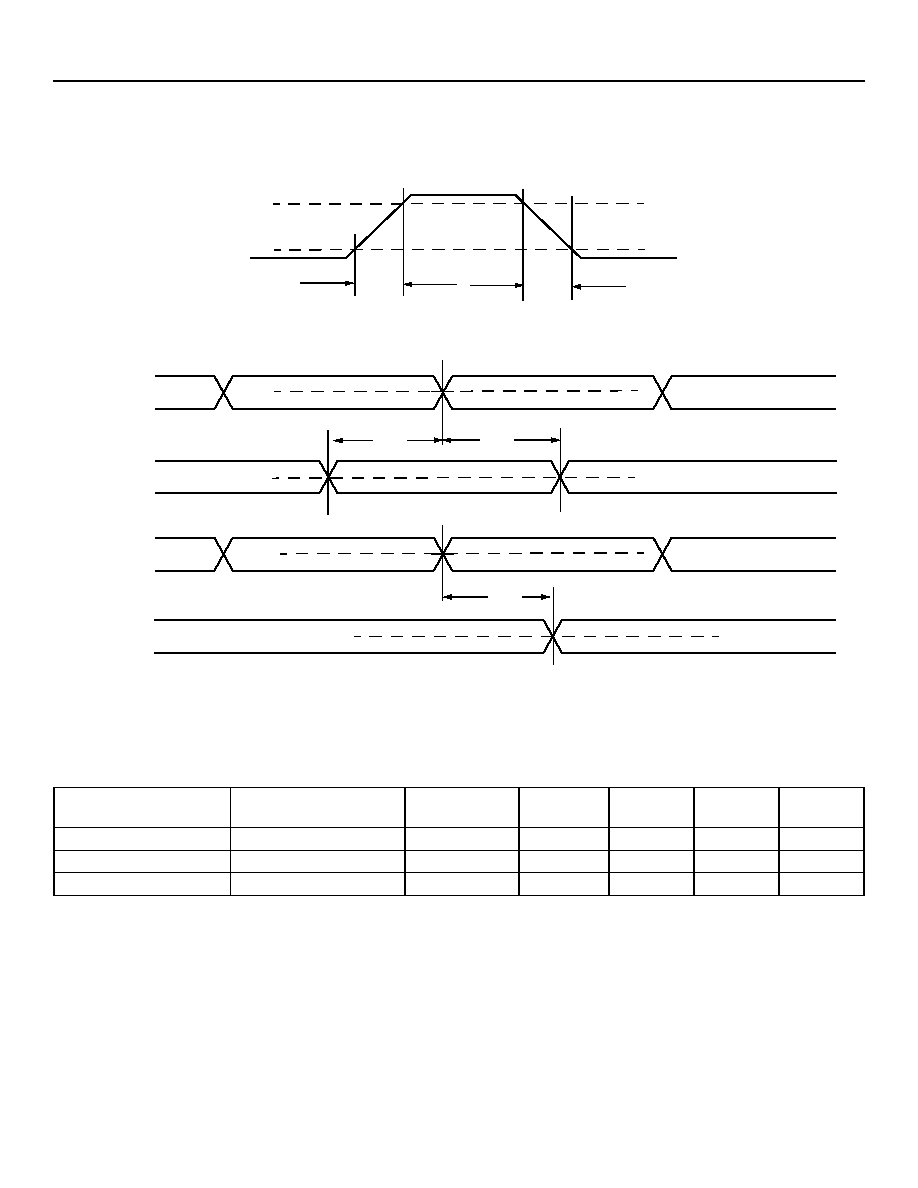

Figure 5-1. TMUX LVDS Signal Rise/Fall Timing

Figure 5-2. TMUX LVDS Clock and Data Timing

Table 5-1. High-Speed Interface Inputs Specifications

Name

Reference

Edge

Rising/Falling

Max Rise

Time (ns)

Max Fall

Time (ns)

Min Setup

(ns)

Min Hold

(ns)

RHSDP/N (622 MHz)*

* Input serial data stream should have minimum eye opening of 0.4 UIp-p, and no more than 60 consecutive bits that have no transitional edge

within one minute. It must meet 100 ps maximum phase variation limit over a 200 ns interval; this translates to a frequency change of 500 ppm.

Asynchronous

—

0.5

—

RHSDP/N (155 MHz)