- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156622 > 4565B2 (LSI CORP) ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 PDF資料下載

參數(shù)資料

| 型號: | 4565B2 |

| 廠商: | LSI CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 封裝: | PLASTIC, BGA-909 |

| 文件頁數(shù): | 15/61頁 |

| 文件大小: | 1691K |

| 代理商: | 4565B2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

4565B Ultramapper Full Transport Retiming Device

Hardware Design Guide, Revision 2

622/155 Mbits/s SONET/SDH x DS3/E3/DS2/DS1/E1

December 17, 2003

22

Agere Systems Inc.

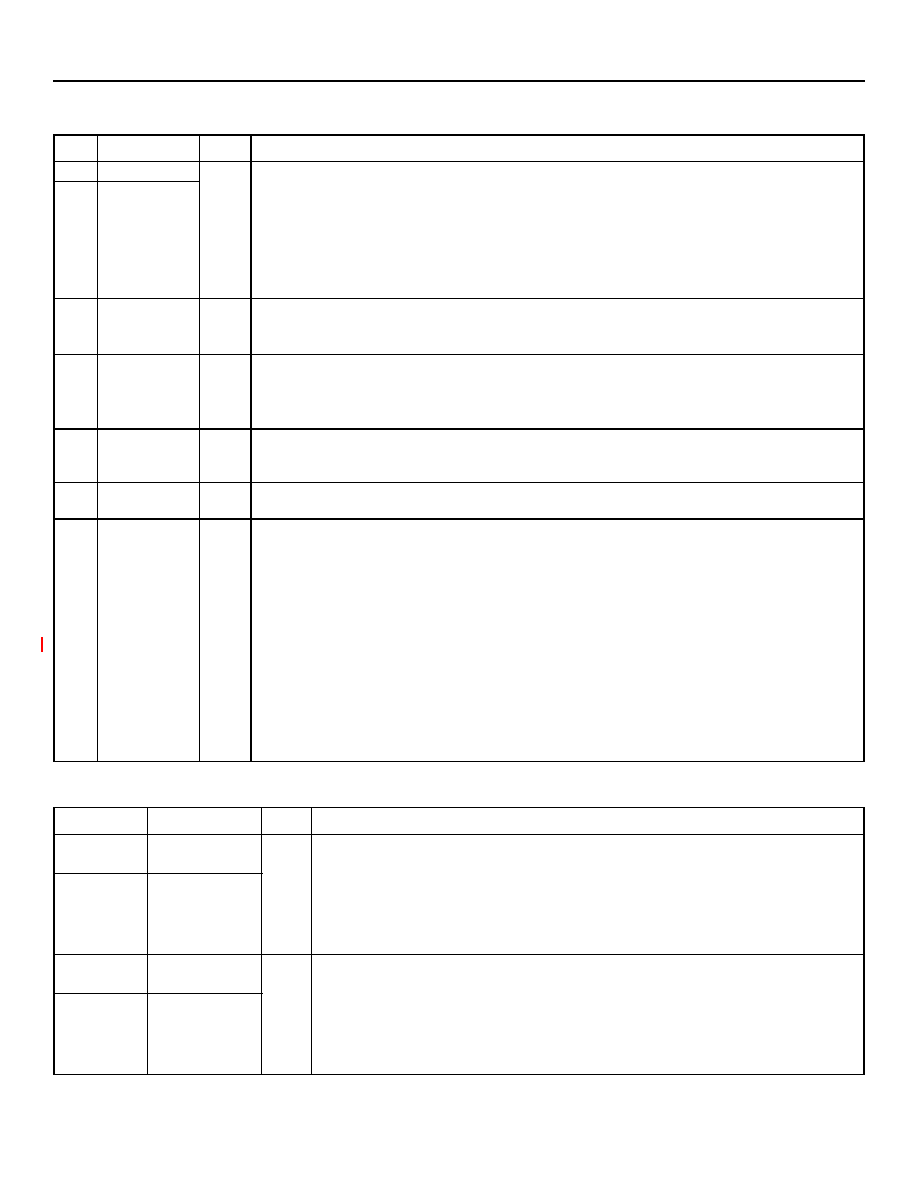

Table 2-6. TMUX Block, Clock and Sync I/O

Pin

Symbol

Type

Name/Description

AN4

THSCP

LIN

Transmit High-Speed Clock. 622/155 MHz input clock for transmit 622/155 Mbits/s data.

Also used as a reference clock for all CDRs. There are five CDR circuits. The high-speed data

and protection high-speed data have CDRs that operate at 155 MHz or 622 MHz. The mate

inputs have three CDRs that operate at 155 MHz. The clock on this pin is also internally rout-

ed to the DS1/E1 framers and is used as an internal master clock.

Note: A 622 MHz clock must be supplied when the device operates in 622 Mbits/s mode. A

155 MHz clock must be supplied when the device operates in 155 Mbits/s mode.

AP4

THSCN

AG9

CTAPTH

—

Center Tap TH. LVDS buffer terminator center tap for THSCP/N. An optional 0.1 F capaci-

tor, connected between CTAP pin and ground, will improve the common-mode rejection of

the LVDS input buffers.

AP22 RHSFSYNCN

O

Receive High-Speed Frame Sync. This output indicates the start of the frame in the high-

speed data input. Only present when a valid frame signal is detected on the RHSDP/N

inputs. It is an active-low pulse with a pulse width almost equal to one E1 clock period, or

approximately 500 ns.

AJ14

RLSCLK

O

Receive Low-Speed Clock. 19.44 MHz receive output clock divided down from either

RHSCP/N or the recovered high-speed clock (when the CDR is used). May be used as a

system timing reference.

AK13

TLSCLK

O

Transmit Low-Speed Clock. 19.44 MHz transmit output clock divided down from

THSCP/N.

AL13

THSSYNC

I/O pd Transmit High-Speed Frame Sync. 2 kHz/8 kHz composite frame sync signal that identi-

fies the locations of the J0, J1-1, J1-2, J1-3 . . . J1-12 , and V1-1 bytes. This signal is used to

align transmit frames before multiplexing.

Note: J0, J1-1, J1-2, and J1-3 . . . J1-12 occur every 125 s. V1-1 occurs every 500 s.

If the register MPU_MASTER_SLAVE = 1, THSSYNC is an output; otherwise, THSSYNC is

an input.

The positive 8 kHz and 2 kHz pulses are synchronized to TLSCLK (in master mode only).

The rising edge is referenced for frame location. For master/slave configuration, the

THSSYNC of all 4565B Ultramapper Full Transport Retiming Devices (up to four) must be

connected together. The master can be one of the 4565B Ultramapper Full Transport Retim-

ing Devices, and it sources the frame sync pulse to other 4565B Ultramapper Full Transport

Retiming Devices. All 4565B Ultramapper Full Transport Retiming Devices can also be con-

figured as slaves and receive frame sync from the external system frame sync.

Table 2-7. STS Cross Connect (STSXC) Block, STS-3/STM-1 Mate Interconnect

Pin

Symbol

Type

Name/Description

AP11, AM9,

AP10

RLSDATAP[3:1] LOUT Receive Low-Speed Data. These pins are only used in 622 Mbits/s applications,

and are used only on the master device. These pins should be connected to the

high-speed data inputs (RHSDP/N) of the slave devices.

This 155 Mbits/s signal uses a SONET structure. The overhead supported are the

A1/A2 and B2 bytes and line RDI. The data is scrambled. Data from the RHSD is

routed via the STSXC.

AP12,

AM10, AN10

RLSDATAN[3:1]

AG11, AN12,

AN11

TLSDATAP[3:1]

LIN

Transmit Low-Speed Data. These pins are only used in 622 Mbits/s applications,

and are used only on the master device. These pins should be connected to the

high-speed data outputs (THSDP/N) of the slave devices. This 155 Mbits/s input re-

ceives data from the slave high-speed outputs.

These inputs have built-in clock and data recovery (CDR). The frame location ex-

pects a fixed relationship to the high-speed transmit frame sync (THSSYNC).

AG12,

AN13, AM11

TLSDATAN[3:1]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 4565B2 | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 45APC180K | 1 ELEMENT, 18 uH, GENERAL PURPOSE INDUCTOR |

| 45APC470K | 1 ELEMENT, 47 uH, GENERAL PURPOSE INDUCTOR |

| 45APC272K | 1 ELEMENT, 2700 uH, GENERAL PURPOSE INDUCTOR |

| 45K101-101H3 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 4565-BLK | 制造商:Pomona Electronics 功能描述:ACCESSORIES, MAXIGRABBER TEST CLIP |

| 4565-BLK-3XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-4XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-L | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-M | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。