- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F200B5 (Intel Corp.) 5V Boot Block Flash Memory(5 V 引導塊閃速存儲器) PDF資料下載

參數(shù)資料

| 型號: | 28F200B5 |

| 廠商: | Intel Corp. |

| 英文描述: | 5V Boot Block Flash Memory(5 V 引導塊閃速存儲器) |

| 中文描述: | 5V的啟動塊閃存(5伏引導塊閃速存儲器) |

| 文件頁數(shù): | 39/44頁 |

| 文件大?。?/td> | 345K |

| 代理商: | 28F200B5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當前第39頁第40頁第41頁第42頁第43頁第44頁

E

5.11

28F200B5, 28F004/400B5, 28F800B5

39

PRELIMINARY

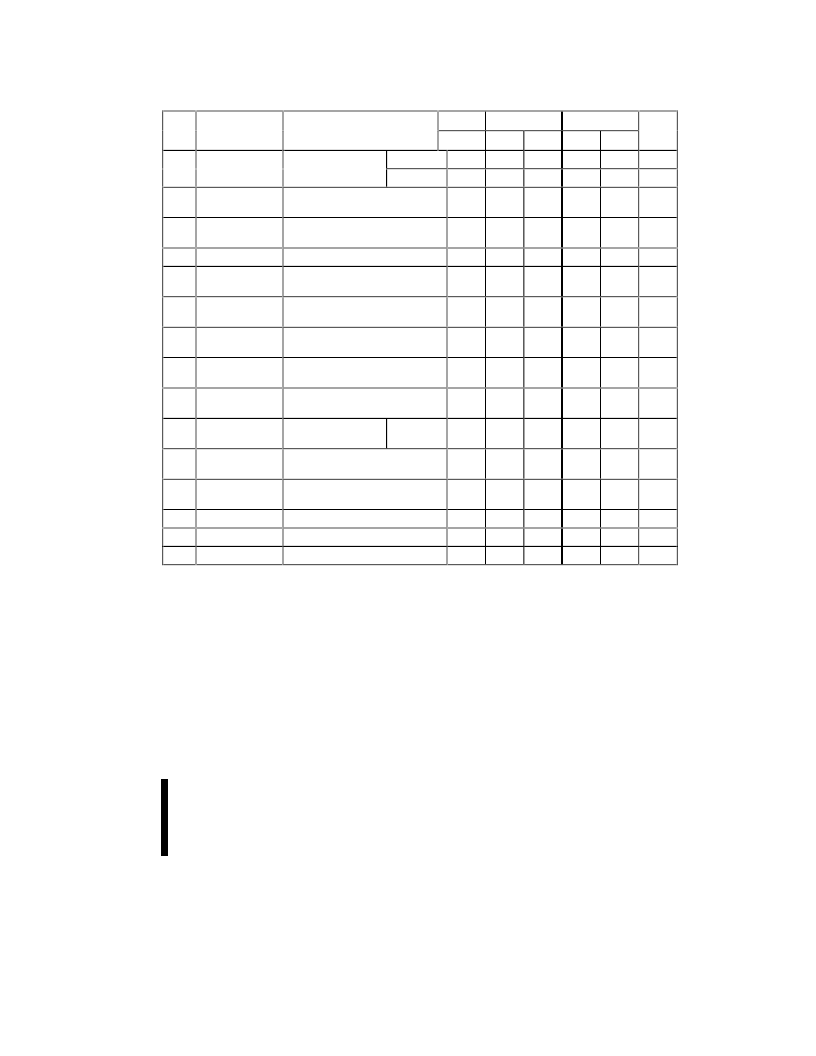

AC Characteristics

—Write Operations—Automotive Temperature

Speed

-80

-90

#

Sym

Parameter

Note

Min

Max

Min

Max

Unit

W0

t

AVAV

Write Cycle Time

2,4 Mbit

80

n/a

ns

8 Mbit

80

90

ns

W1

t

PHWL

(t

PHEL

)

RP# High Recovery to WE#

(CE#) Going Low

450

450

ns

W2

t

ELWL

(t

WLEL

)

CE# (WE#) Setup to WE#

(CE#) Going Low

0

0

ns

W3

t

WP

t

DVWH

(t

DVEH

)

Write Pulse Width

9

60

60

ns

W4

Data Setup to WE# (CE#)

Going High

4

60

60

ns

W5

t

AVWH

(t

AVEH

)

Address Setup to WE# (CE#)

Going High

3

60

60

ns

W6

t

WHEH

(t

EHWH

)

CE# (WE#) Hold from WE#

(CE#) High

0

0

ns

W7

t

WHDX

(t

EHDX

)

Data Hold from WE# (CE#)

High

4

0

0

ns

W8

t

WHAX

(t

EHAX

)

Address Hold from WE# (CE#)

High

3

0

0

ns

W9

t

WPH

Write Pulse Width

High

V

CC

= 5 V

±

5%

10

10

ns

W10

t

PHHWH

(t

PHHEH

)

RP# V

HH

Setup to WE# (CE#)

Going High

6,8

100

100

ns

W11

t

VPWH

(t

VPEH

)

V

PP

Setup to WE# (CE#) Going

High

5,8

100

100

ns

W12

t

QVPH

t

QVVL

t

PHBR

RP# V

HH

Hold from Valid SRD

V

PP

Hold from Valid SRD

Boot Block Lock Delay

6,8

0

0

ns

W13

5,8

0

0

ns

W14

7,8

100

100

ns

NOTES:

1. Read timing characteristics during program and erase operations are the same as during read-only operations. Refer to AC

Characteristics

—Read-Only Operations.

2. The on-chip WSM completely automates program/erase operations; program/erase algorithms are now controlled internally

which includes verify operations.

3. Refer to command definition table for valid A

IN

. (Table 7)

4. Refer to command definition table for valid D

IN

. (Table 7)

5. Program/erase durations are measured to valid SRD data (successful operation, SR.7 = 1).

6. For boot block program/erase, RP# should be held at V

HH

or WP# should be held at V

IH

until operation completes

successfully.

7. Time t

PHBR

is required for successful locking of the boot block.

8. Sampled, but not 100% tested.

9. Write pulse width (t

) is defined from CE# or WE# going low (whichever goes low last)

to CE# or WE# going high

(whichever goes high first). Hence, t

WP

= t

WLWH

= t

ELEH

= t

WLEH

= t

ELWH

.

10. Write pulse width high (t

) is defined from CE# or WE# going high (whichever goes high first)

to CE# or WE# going low

(whichever goes low first). Hence, t

WPH

= t

WHWL

= t

EHEL

= t

WHEL

= t

EHWL

.

相關PDF資料 |

PDF描述 |

|---|---|

| 28F200BV-TB | 2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F200BX | 2-MBIT (128K x 16, 256K x 8) BOOT BLOCK FLASH MEMORY FAMILY |

| 28F200BX-TB | 2-MBIT (128K x 16, 256K x 8) BOOT BLOCK FLASH MEMORY FAMILY |

| 28F200BX-B | 5V or Adjustable, Low-Voltage, Step-Up DC-DC Controller |

| 28F200BX-T | Evaluation Kit for the MAX608 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 28F200BL-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT (128K x 16. 256K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F200BL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT (128K x 16. 256K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F200BL-T/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| 28F200BL-TB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:2-MBIT (128K x 16, 256K x 8)LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F200BV-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-MBIT SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

發(fā)布緊急采購,3分鐘左右您將得到回復。