- 您現在的位置:買賣IC網 > PDF目錄359354 > VDP3108 (MICRONAS SEMICONDUCTOR HOLDING AG) Single-Chip Video Processor PDF資料下載

參數資料

| 型號: | VDP3108 |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Single-Chip Video Processor |

| 中文描述: | 單芯片視頻處理器 |

| 文件頁數: | 24/61頁 |

| 文件大?。?/td> | 2638K |

| 代理商: | VDP3108 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

VDP 3108

ADVANCE INFORMATION

MICRONAS INTERMETALL

24

3. Serial Interface

3.1. I

2

C Bus Interface

Communication between the VDP and the external con-

troller is done via I

2

C bus. The VDP has an I

2

C bus slave

interface and uses I

2

C clock synchronization to slow

down the interface if required. The I

2

C bus interface

uses one level of subaddress: one I

2

C bus address is

used to address the IC and a subaddress selects one of

the internal registers. The I

2

C bus chip address is given

below:

A6

A5

A4

A3

A2

A1

A0

R/W

1

0

0

0

1

0

1

0/1

The registers of the VDP have 8 or 16 bit data size; 16

bit registers are accessed by reading/writing two 8 bit

data words.

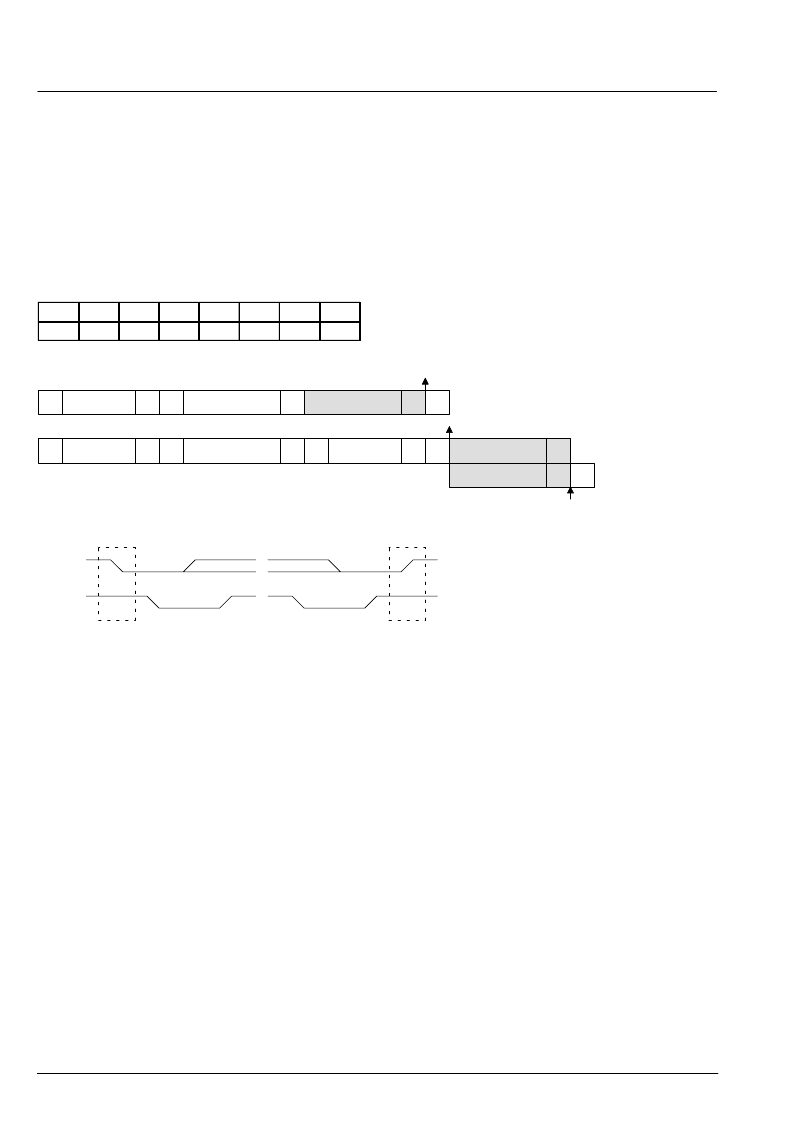

Figure 3–1 shows I

2

C bus protocols for read and write

operations of the interface; the read operation requires

an extra start condition and repetition of the chip address

with read command set.

W

P

1 or 2 byte Data

W

high byte Data

S

S

Ack

Ack

Ack

Ack

0111 1100

0111 1100

R

S

Ack

SDA

SCL

1

0

S

P

P

low byte Data

Ack

W

R

Ack

Nak

S

P

=

=

=

=

=

=

0

1

0

1

Start

Stop

Ack

Nak

Fig. 3–1:

I

2

C Bus Protocols

1000 101

1000 101

1000 101

I

2

C write access

subaddress 7c

I

2

C read access

subaddress 7c

3.2. Control and Status Registers

Table 3–1 gives definitions of the VDP control and status

registers. The number of bits indicated for each register

in the table is the number of bits implemented in hard-

ware, i.e. a 9-bit register must always be accessed us-

ing two data bytes but the 7 MSB will be don’t care on

write operations and 0 on read operations. Write regis-

ters that can be read back are indicated in the following

table.

Functions implemented by software in the on-chip con-

trol microprocessor (FP) are explained elsewhere.

A hardware reset initializes all control registers to 0. The

automatic chip initialization loads a selected set of regis-

ters with the default values given in Table 3–1.

The register modes given in Table 3–1 are:

w

w/r

r

v

write only register

write/read data register

read data from VDP

register is latched with vertical sync

The mnemonics used in the Intermetall VDP demo soft-

ware are given in the last column.

相關PDF資料 |

PDF描述 |

|---|---|

| VDP3130Y | Video Processor Family |

| VDP31XXB | Video Processor Family |

| VDP3108PR | Consumer IC |

| VDSGLD_38.88 | TRANS PREBIASED PNP 200MW SOT23 |

| VDSL5100I | TVS 400W 43V UNIDIRECT SMA |

相關代理商/技術參數 |

參數描述 |

|---|---|

| VDP3108B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3108PR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

| VDP3112B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3116B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3120B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。