- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383876 > T7698 (Lineage Power) Quad T1/E1 Line Interface and Octal T1/E1 Monitor(四T1/E1線接口和八T1/E1監(jiān)控器) PDF資料下載

參數(shù)資料

| 型號: | T7698 |

| 廠商: | Lineage Power |

| 英文描述: | Quad T1/E1 Line Interface and Octal T1/E1 Monitor(四T1/E1線接口和八T1/E1監(jiān)控器) |

| 中文描述: | 四T1/E1線路接口和八路的T1/E1監(jiān)視器(四個T1/E1線接口和八T1/E1的監(jiān)控器) |

| 文件頁數(shù): | 19/112頁 |

| 文件大小: | 1359K |

| 代理商: | T7698 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

Data Sheet

January 1999

T7698 Quad T1/E1 Line Interface and Octal T1/E1 Monitor

19

Lucent Technologies Inc.

Microprocessor Interface

(continued)

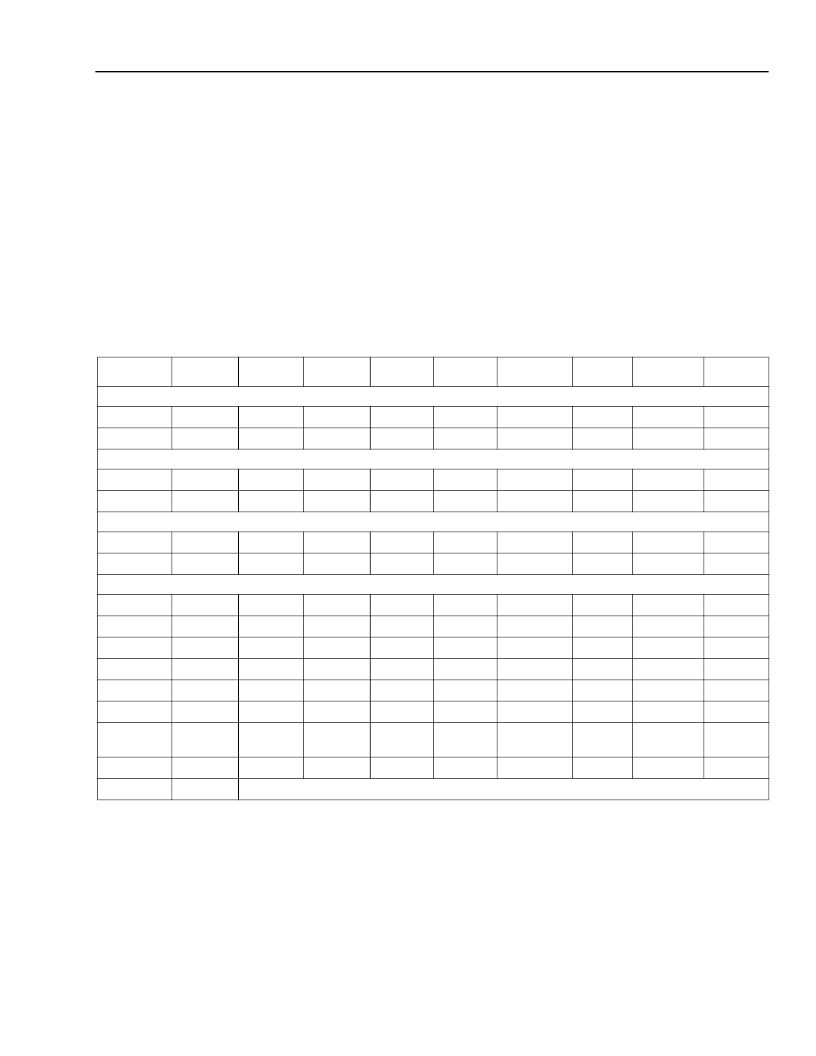

Microprocessor Interface Register Architecture

The register bank architecture of T7698 consists of a primary register bank for the quad line interface unit and sec-

ondary register banks for the receive frame monitor [1—8] and FDL [1—8]. The primary register bank consists of

sixteen 8-bit registers comprising the alarm, control, and configuration registers for the quad line interface unit.

Register 13 (1101) of the primary register bank is a global index register used to access the secondary registers

(this is needed because the microprocessor address bus is only 4 bits wide). The default (reset) value of register

13 is 00 (hexadecimal) allowing writes to and reads from the primary (LIU) register bank. Writing 01 (hexadecimal)

through 08 (hexadecimal) to register 13 allows access to frame monitors [1—8], respectively, and writing 11 (hexa-

decimal) through 18 (hexadecimal) allows access to FDL [1—8], respectively.

Table 6 shows the primary register bank and Figure 3 shows the secondary register bank architecture.

* Device version determines reset state of bit. 0 = V1 and V2; 1 = V3.

Notes:

A numerical suffix appended to the bit name identifies the channel number.

Bits shown in parentheses indicate the state forced during a reset condition.

All registers must be configured by the user before the device can operate as required for the particular application.

Table 6. Primary (LIU) Register Bank

Designation

Address

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Alarm Registers (Read Only)

0

0000

LOTC2

TDM2

DLOS2

ALOS2

LOTC1

TDM1

DLOS1

ALOS1

1

0001

LOTC4

TDM4

DLOS4

ALOS4

LOTC3

TDM3

DLOS3

ALOS3

Alarm Mask Registers (Read/Write)

2

0010

MLOTC2

MTDM2

MDLOS2

MALOS2

MLOTC1

MTDM1

MDLOS1

MALOS1

3

0011

MLOTC4

MTDM4

MDLOS4

MALOS4

MLOTC3

MTDM3

MDLOS3

MALOS3

Global Control Registers (Read/Write)

4

0100

HIGHZ4 (1)

HIGHZ3 (1)

HIGHZ2 (1) HIGHZ1 (1)

ICTMODE (0)

LOSSTD

SWRESET(0) GMASK (1)

5

0101

LOSSD

ACM

ALM

DUAL

CODE

JAT

JAR

CDR

Channel Configuration Registers (Read/Write)

6

0110

EQA1

EQB1

EQC1

LOOPA1

LOOPB1

XAIS1

MASK1

PWRDN1

7

0111

EQA2

EQB2

EQC2

LOOPA2

LOOPB2

XAIS2

MASK2

PWRDN2

8

1000

EQA3

EQB3

EQC3

LOOPA3

LOOPB3

XAIS3

MASK3

PWRDN3

9

1001

EQA4

EQB4

EQC4

LOOPA4

LOOPB4

XAIS4

MASK4

PWRDN4

10

1010

0

0

0

0

0

0

0

0

11

1011

0

CODE3

0

CODE4

0

0

0

0

12

1100

CODE1

CODE2

JABW0

(0)

PHIZALM

(0)

PRLALM

(0)

PFLALM

(0)

RCVAIS

(0)

ALTIMER

(0)

13

1101

(VERSION)

*

0

0

RI4

RI3

RI2

RI1

RI0

14—15

1110—1111

RESERVED

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7705A | SUPPLY-VOLTAGE SUPERVISORS |

| T8100A | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線時間段交換機) |

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線時隙交換機) |

| T8102 | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線時隙交換機) |

| T8105 | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線時隙交換機) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T77 | 制造商:Thomas & Betts 功能描述:2-1/2"CONDUIT BODY,IRON,T,F-7 制造商:Cooper Crouse-Hinds 功能描述: 制造商:Thomas & Betts 功能描述:Fittings T-Fitting 2.5inch Non-Thread Iron |

| T7700 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Core2 Duo Processors and Core2 Extreme Processors for Platforms Based on Mobile 965 Express Chipset Family |

| T77000150 | 制造商:Assembly Value Added 功能描述: |

| T7705102CA | 制造商:Texas Instruments 功能描述: |

| T7705A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SUPPLY-VOLTAGE SUPERVISORS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。