- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372122 > SC28L202 (NXP Semiconductors N.V.) Dual universal asynchronous receiver/transmitter DUART PDF資料下載

參數(shù)資料

| 型號(hào): | SC28L202 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Dual universal asynchronous receiver/transmitter DUART |

| 中文描述: | 雙路通用異步接收器/發(fā)送器杜阿爾特 |

| 文件頁數(shù): | 58/77頁 |

| 文件大?。?/td> | 531K |

| 代理商: | SC28L202 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當(dāng)前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

Philips Semiconductors

Objective specification

SC28L202

Dual UART

2000 Feb 10

52

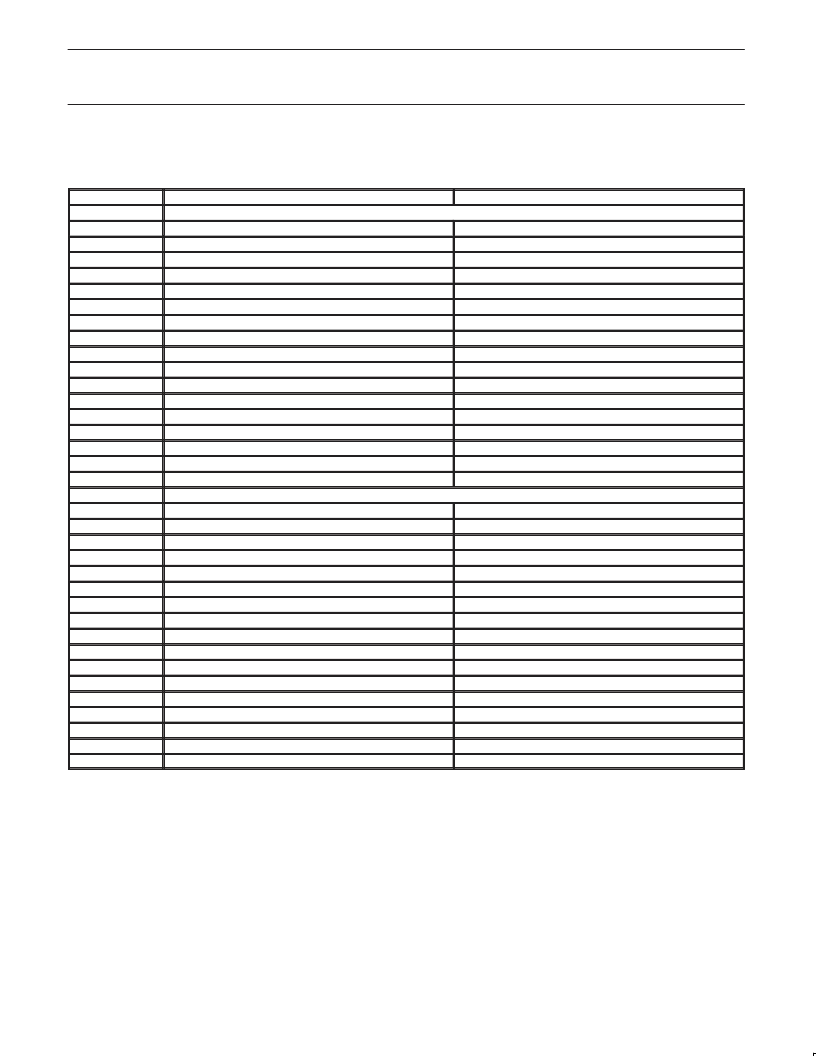

REGISTER MAP (BASED ON 28L92)

NOTE: The register maps for channels A and B (UARTs A and B) contain some control registers that configure the entire chip.

These are

denoted by a ”

” symbol

A(6:0)

READ

EXTENSION

010 0000 (0x20)

Mode Register 0 (MR0 A)

NEW ADDRESS

010 0001 (0x21)

Mode Register 1 (MR1 A)

NEW ADDRESS

010 0010 (0x22)

Mode Register 2 (MR2 A)

NEW ADDRESS

010 0011 (0x23)

Mode Register 3 (MR3 A)

NEW ADDRESS

010 0100 (0x24)

Counter/Timer Clock Source (CTCS 0)

010 0101 (0x25)

Interrupt Status Register (ISR A)

010 0110 (0x26)

Programmable BRG Preset Lower (PBRGPL 0)

010 0111 (0x27)

Programmable BRG Preset Upper (PBRGPU 0)

WRITE

Mode Register 0 (MR0 A)

NEW ADDRESS

Mode Register 1 (MR1 A)

NEW ADDRESS

Mode Register 2 (MR2 A)

NEW ADDRESS

Mode Register 3 (MR3 A)

NEW ADDRESS

Counter/Timer Clock Source (CTCS 0)

Interrupt Mask Register (IMR A)

Programmable BRG Preset Lower (PBRGPL 0)

Programmable BRG Preset Upper (PBRGPU 0)

010 1000 (0x28)

010 1001 (0x29)

010 1010 (0x2A)

010 1011 (0x2B)

010 1100 (0x2C)

010 1101 (0x2D)

010 1110 (0x2E)

010 1111 (0x2F)

Mode Register 0 (MR0 B)

NEW ADDRESS

Mode Register 1 (MR1 B)

NEW ADDRESS

Mode Register 2 (MR2 B)

NEW ADDRESS

Mode Register 3 (MR3 B)

NEW ADDRESS

Counter/Timer Clock Source (CTCS 1)

Interrupt Status Register (ISR B)

Mode Register 0 (MR0 B)

NEW ADDRESS

Mode Register 1 (MR1 B)

NEW ADDRESS

Mode Register 2 (MR2 B)

NEW ADDRESS

Mode Register 3 (MR3 B)

NEW ADDRESS

Counter/Timer Clock Source (CTCS 1)

Interrupt Mask Register (IMR B)

011 0000 (0x30)

011 0001 (0x31)

011 0010 (0x32)

011 0011 (0x33)

011 0100 (0x34)

011 0101 (0x35)

011 0110 (0x36)

011 0111 (0x37)

Receiver Clock Select Register (RxCSR A)

Transmitter Clock Select Register (TxCSR A)

Input Port Change Interrupt Enable (IPCE A)

Programmable BRG Clock Source (PBRGCS)

Receiver Clock Select Register (RxCSR A)

Transmitter Clock Select Register (TxCSR A)

Input Port Change Interrupt Enable (IPCE A)

Programmable BRG Clock Source (PBRGCS)

Programmable BRG Preset Lower (PBRGPL 1)

Programmable BRG Preset Upper (PBRGPU 1)

Programmable BRG Preset Lower (PBRGPL 1)

Programmable BRG Preset Upper (PBRGPU 1)

011 1000 (0x38)

011 1001 (0x39)

011 1010 (0x3A)

011 1011 (0x3B)

011 1100 (0x3C)

011 1101 (0x3D)

011 1110 (0x3E)

011 1111 (0x3F)

Receiver Clock Select Register (RxCSR B)

Transmitter Clock Select Register (TxCSR B)

Input Port Change Interrupt Enable (IPCE B)

Receiver Clock Select Register (RxCSR B)

Transmitter Clock Select Register (TxCSR B)

Input Port Change Interrupt Enable (IPCE B)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC28L202A1B | Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1D | Dual universal asynchronous receiver/transmitter DUART |

| SC431CS8DE2 | Analog IC |

| SC431CS8DE3 | Analog IC |

| SC431CS8DF1 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC28L202A1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1B | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1D | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1DGG | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS 256B FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L202A1DGG,112 | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。