- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372112 > SAA5647HL (NXP Semiconductors N.V.) Enhanced TV microcontrollers with On-Screen Display (OSD)(帶全屏顯示的增強型TV控制器) PDF資料下載

參數(shù)資料

| 型號: | SAA5647HL |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Enhanced TV microcontrollers with On-Screen Display (OSD)(帶全屏顯示的增強型TV控制器) |

| 中文描述: | 與微控制器在強化電視屏幕顯示(OSD)(帶全屏顯示的增強型電視控制器) |

| 文件頁數(shù): | 8/112頁 |

| 文件大小: | 436K |

| 代理商: | SAA5647HL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

2000 Jun 30

8

Philips Semiconductors

Objective specification

Enhanced TV microcontrollers with

On-Screen Display (OSD)

SAA56xx

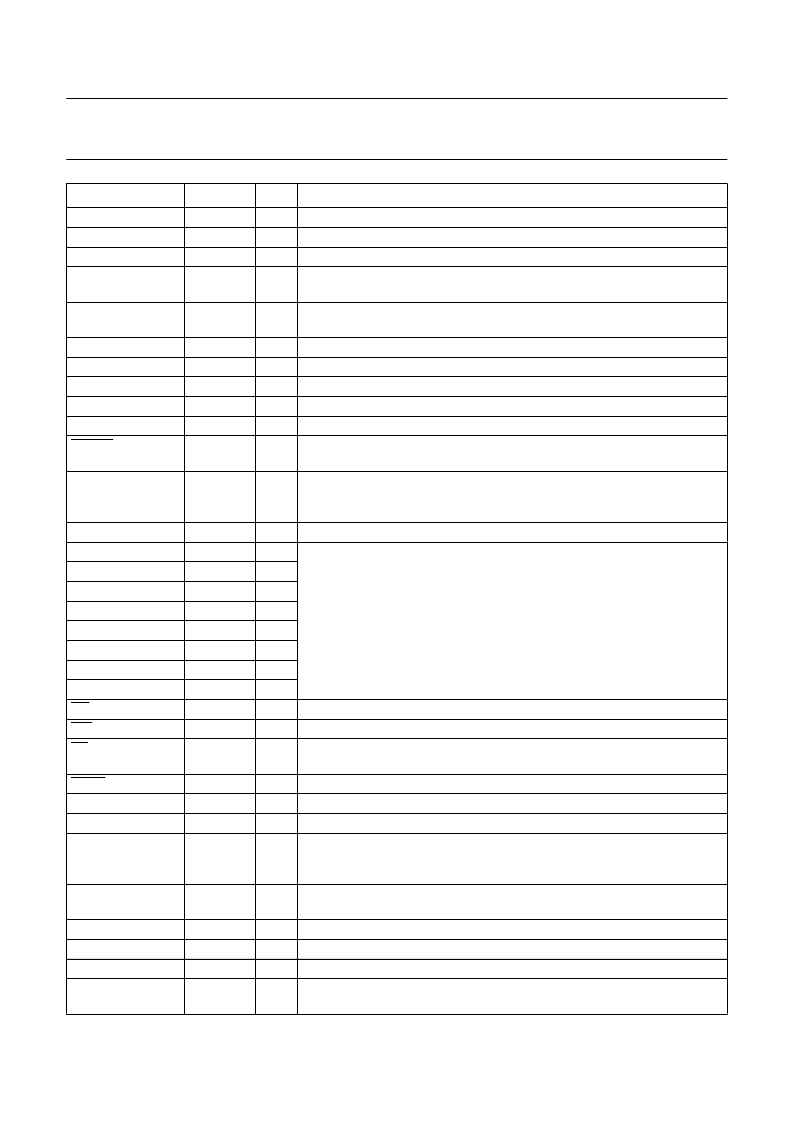

G

R

VDS

HSYNC

47

48

52

53

O

O

O

I

pixel rate output of the GREEN colour information

pixel rate output of the RED colour information

video/data switch push-pull output for dot rate fast blanking

Schmitt triggered input for a TTL-level version of the horizontal sync pulse;

the polarity of this pulse is programmable by register bit TXT1.H POLARITY.

Schmitt triggered input for a TTL-level version of the vertical sync pulse; the

polarity of this pulse is programmable by register bit TXT1.V POLARITY.

periphery ground

+3.3 V core power supply

crystal oscillator ground

12 MHz crystal oscillator input

12 MHz crystal oscillator output

If the reset input is LOW for at least 24 crystal oscillator periods while the

oscillator is running, the device is reset (internal pull-up).

If the reset input is HIGH for at least 24 crystal oscillator periods while the

oscillator is running, the device is reset. This pin should be connected to

V

DDC

via a capacitor if an active HIGH reset is required (internal pull-down).

+3.3 V periphery power supply

Port 1.

8-bit programmable bidirectional port with alternative functions.

VSYNC

55

I

V

SSP

V

DDC

OSCGND

XTALIN

XTALOUT

RESET

12, 60

63

69

70

71

72

I

O

I

RESET

73

I

V

DDP

P1.0/INT1

P1.1/T0

P1.2/INT0

P1.3/T1

P1.6/SCL0

P1.7/SDA0

P1.4/SCL1

P1.5/SDA1

RD

WR

EA

75

76

78

79

80

81

82

83

84

9

10

14

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

I

P1.0/INT1 is external interrupt 1 which can be triggered on the rising and

falling edge of the pulse; P1.1/T0 is Timer/counter 0; P1.2/INT0 is external

interrupt 0; P1.3/T1 is Timer/counter 1; P1.6/SCL0 is the serial clock input

for the I

2

C-bus; P1.7/SDA0 is the serial data port for the I

2

C-bus; P1.4/SCL1

is the serial clock input for the I

2

C-bus; P1.5/SDA1 is the serial data port for

the I

2

C-bus.

read control signal to external data memory

write control signal to external data memory

control signal used to select external (low) or internal (high) program

memory (internal pull-up)

enable signal for external program memory

external latch enable signal; active HIGH

address lines A0 to A7 multiplexed with data lines D0 to D7.

address lines A0 to A7

PSEN

ALE

AD0 to AD7

A0 to A7

19

20

O

O

I/O

O

85 to 92

49, 40, 39,

38, 27, 26,

23, 15

67 to 64,

37, 36, 8

7, 77, 3

68

74

33

A8 to A14

O

address lines A8 to A14

A15_LN to A17_LN

MOVX_WR

MOVX_RD

A15_BK

O

O

O

O

address lines A15 to A17; note 1

MOVX Write for Hitex 80C51 emulation (internal MOVX Write instruction)

MOVX Read for Hitex 80C51 emulation (internal MOVX Read instruction)

address line A15 when using ROMBK outputs for external program ROM

access

SYMBOL

PIN

TYPE

DESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| SAA5667HL | Enhanced TV microcontrollers with On-Screen Display (OSD)(帶全屏顯示的增強型TV控制器) |

| SAA5697HL | Enhanced TV microcontrollers with On-Screen Display (OSD) |

| SAA5675HL | Enhanced TV microcontrollers with On-Screen Display (OSD) |

| SAA567X | Enhanced TV microcontrollers with On-Screen Display (OSD) |

| SAA5695HL | Enhanced TV microcontrollers with On-Screen Display (OSD) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SAA5665 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced TV microcontrollers with On-Screen Display OSD |

| SAA5665HL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced TV microcontrollers with On-Screen Display OSD |

| SAA5667 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced TV microcontrollers with On-Screen Display OSD |

| SAA5667HL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced TV microcontrollers with On-Screen Display OSD |

| SAA5675HL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced TV microcontrollers with On-Screen Display (OSD) |

發(fā)布緊急采購,3分鐘左右您將得到回復。