- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372108 > SAA2502 (NXP Semiconductors N.V.) ISO/MPEG Audio Source Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAA2502 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | ISO/MPEG Audio Source Decoder |

| 中文描述: | 的ISO / MPEG音頻信源解碼器 |

| 文件頁(yè)數(shù): | 8/64頁(yè) |

| 文件大?。?/td> | 318K |

| 代理商: | SAA2502 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

1997 Nov 17

8

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.2.1

E

XTERNAL SAMPLE CLOCK

In applications where a 256

×

f

s

sample clock is available,

the use of external crystals may be avoided by putting the

SAA2502 clock generator module in ‘external sample

clock mode’. Such mode setting may be realized by setting

control flag FSCINP of the control interface. In this event

the sample clock has to be provided to the FSCLKIN clock

input. If sample rate switching should be supported,

required clock frequency changes are the responsibility of

the application. After such a clock frequency change,

enforcement of a soft reset is advised.

In external sample clock mode (and only in that mode) the

clock generator module is able to accept a 384

×

f

s

sample

clock input. If that mode of operation is desired the control

flag FSC384 should be set.

The FSCLK output is normally disabled in this mode.

If enabled (by setting control flag FSCENA) FSCLK will

produce a buffered copy of FSCLKIN.

X22IN, X22OUT, REFCLK and PHDIF are not used in this

mode. X22IN and REFCLK should be connected to GND

or V

DD

.

MCLKIN is used to provide the (free running) master clock.

This may either be achieved by applying a correct clock

signal to MCLKIN or by connecting a crystal between

MCLKIN and MCLKOUT. In external sample clock mode

(and only in that mode) the master clock may deviate from

24.576 MHz. The master clock frequency value required

depends on the state of pin MCLK24 (see Table 2).

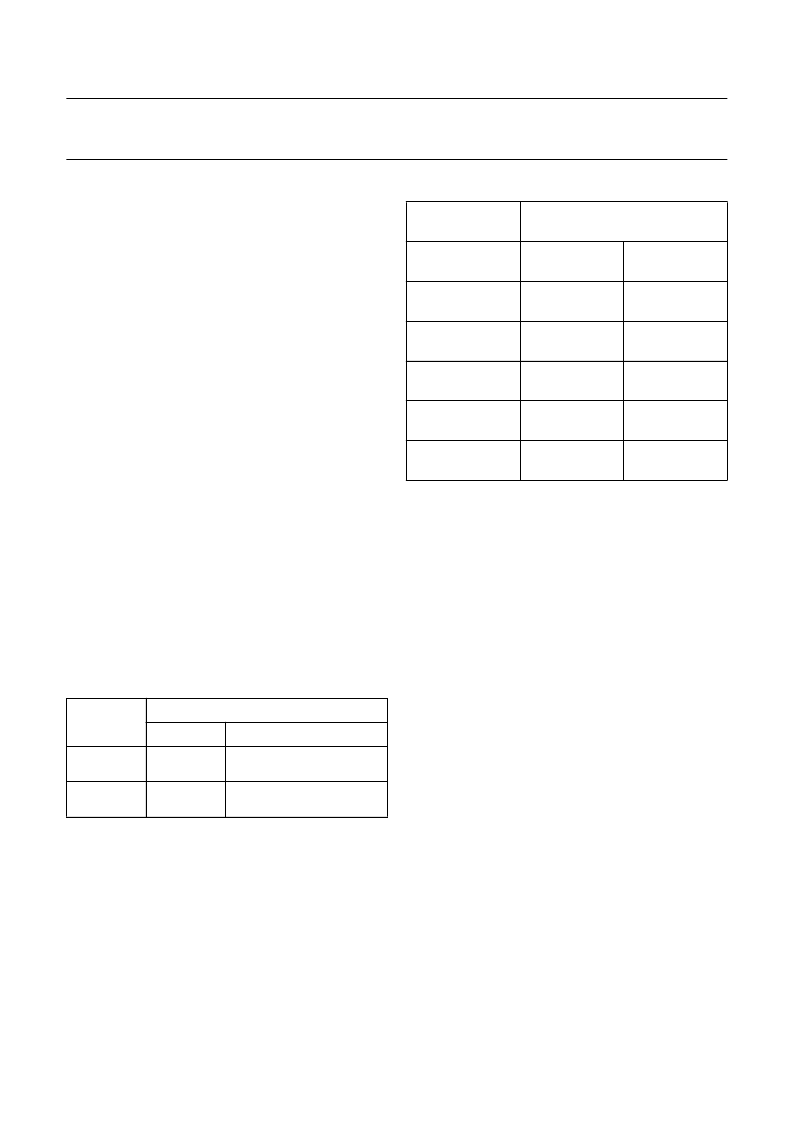

Table 2

Master clock frequency setting by MCLK24

7.2.2

F

REE RUNNING INTERNAL SAMPLE CLOCK

This is the default mode of operation: 256

×

f

s

for all six

supported sample rates is generated internally from the

clock frequencies supplied to MCLKIN (24.576 MHz) and

X22IN (22.5792 MHz) as shown in Table 3.

MCLK24

FREQUENCY

MINIMUM

256

×

f

s

MAXIMUM

GND

12.288 MHz

(256

×

48 kHz)

24.576 MHz

(512

×

48 kHz)

V

DD

512

×

f

s

Table 3

Internal sample clock (default mode)

Note

1.

Asymmetrical FSCLK.

The main advantage of this mode is that the SAA2502

determines automatically which sampling rate is active

from the sampling rate setting of the input data bit stream,

and then selects either MCLKIN or X22IN divided by the

correct number as the sample clock source.

Therefore this mode is particularly suited in applications

supporting dynamically varying sampling rates.

The required clocks may either be applied to MCLKIN

(respectively to X22IN) or be generated by connecting a

crystal between MCLKIN and MCLKOUT (respectively

between X22IN and X22OUT).

The recommended crystal oscillator configuration is

shown in Fig.3. The specified component values only

apply to crystals with a low equivalent series resistance

of <40

.

FSCLKIN, REFCLK and PHDIF are not used in this mode

(FSCLKIN and REFCLK should be connected to V

SS

or

V

DD

). MCLK24 has to be connected to V

DD

, while the

control flags FSCINP and FSC384 should be left in their

default (cleared) states. If the FSCLK output is enabled (by

setting control flag FSCENA) FSCLK will produce a

buffered version of 256

×

f

s

.

SAMPLE

FREQUENCY

256

×

48 kHz

RESULTANT FREQUENCIES

(MHz)

12.288

256

×

44.1 kHz

11.2896

256

×

32 kHz

8.192

(1)

256

×

24 kHz

6.144

256

×

22.05 kHz

5.6448

256

×

16 kHz

4.096

2

24.576

2

22.5792

3

24.576

4

24.576

4

22.5792

6

24.576

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA2502H | ISO/MPEG Audio Source Decoder |

| SAA2503 | MPEG2 audio decoder(MPEG2 音頻譯碼器) |

| SAA2503HT | MPEG2 audio decoder |

| SAA2505H-M1 | Digital multi-channel audio IC DUET |

| SAA2505 | Digital multi-channel audio IC DUET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA2502H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ISO/MPEG Audio Source Decoder |

| SAA2503 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:MPEG2 audio decoder |

| SAA2503HT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:MPEG2 audio decoder |

| SAA2505 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital multi-channel audio IC DUET |

| SAA2505H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital multi-channel audio IC DUET |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。