- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368097 > PPC440SP-RNC667C (APPLIEDMICRO INC) PowerPC 440SP Embedded Processor PDF資料下載

參數(shù)資料

| 型號: | PPC440SP-RNC667C |

| 廠商: | APPLIEDMICRO INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PowerPC 440SP Embedded Processor |

| 中文描述: | 32-BIT, 667 MHz, RISC PROCESSOR, PBGA783 |

| 封裝: | 29 X 29 MM, 1 MM PITCH, ROHS COMPLIANT, PLASTIC, FCBGA-783 |

| 文件頁數(shù): | 76/85頁 |

| 文件大小: | 615K |

| 代理商: | PPC440SP-RNC667C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當(dāng)前第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

PowerPC 440SP Embedded Processor

76

AMCC Proprietary

Revision 1.23 - Sept 26, 2006

Data Sheet

DDR SDRAM I/O Specifications

The DDR SDRAM controller times its operation with internal PLB clock signals and generates MemClkOut0 from

the PLB clock. The PLB clock is an internal signal that cannot be directly observed. However MemClkOut0 is the

same frequency as the PLB clock signal and is in phase with the PLB clock signal.

Note:

MemClkOut0 can be advanced with respect to the PLB clock by means of the SDRAM0_CLKTR

programming register. In a typical system, users advance MemClkOut by 90×. This depends on the specific

application and requires a thorough understanding of the memory system in general (refer to the DDR

SDRAM controller chapter in the

PPC440SP Embedded Processor User’s Manual

).

In the following sections, the label MemClkOut0(0) refers to MemClkOut0 when it has not been phase-shifted, and

MemClkOut0(90) refers to MemClkOut0 when it has been phase-advanced 90

°

. Advancing MemClkOut0 by 90

°

creates a 3/4 cycle setup time and 1/4 cycle hold time for the address and control signals in relation to

MemClkOut0(90). The rising edge of MemClkOut0(90) aligns with the first rising edge of the DQS signal.

The following DDR data is generated by means of

simulation

and includes logic, driver, package RLC, and lengths.

It is

not

to be used as a circuit design recommendation. Values are calculated over best case and worst case

processes with speed, temperature, and voltage as follows:

Best Case = Fast process, -40×C, +1.6V

Worst Case = Slow process, +85×C, +1.4V

Note:

In all the following DDR tables and timing diagrams,

minimum

values are measured under

best

case

conditions and

maximum

values are measured under

worst

case conditions.

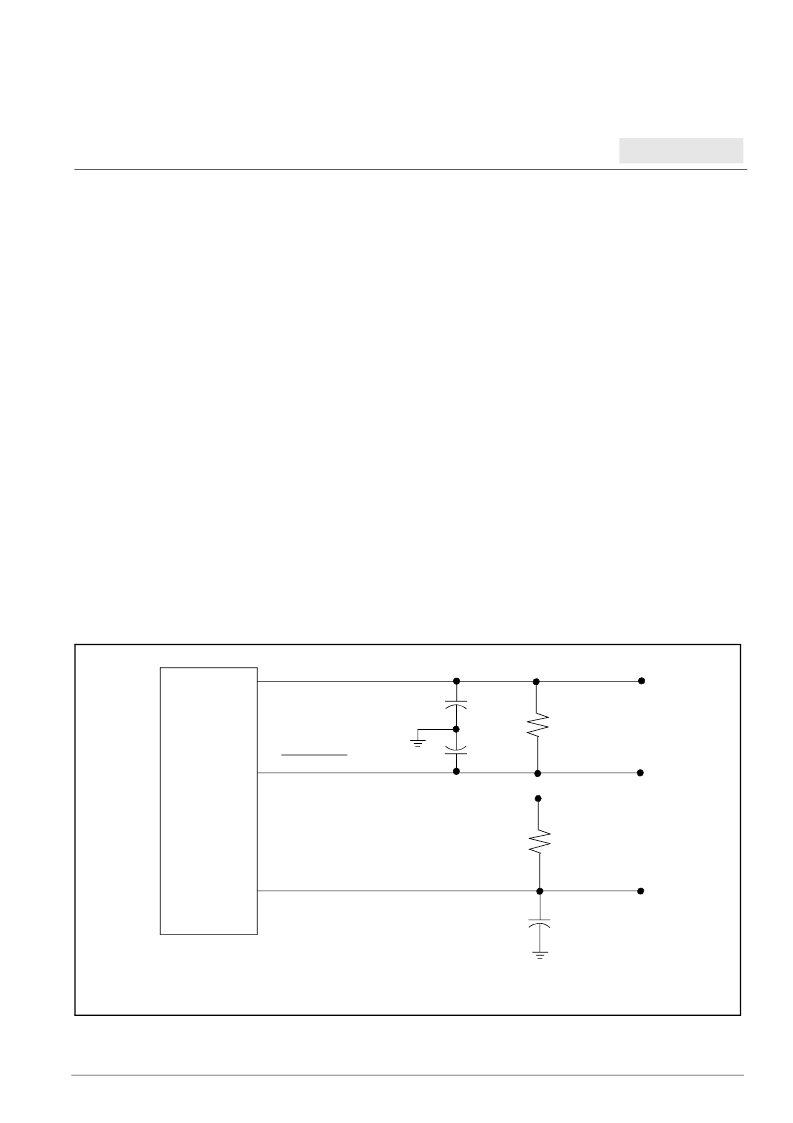

The signals are terminated as indicated in the figure below for the DDR timing data in the following sections.

Figure 7. DDR SDRAM Simulation Signal Termination Model

10pF

10pF

MemClkOut0

MemClkOut0

120W

50W

30pF

Addr/Ctrl/Data/DQS

V

TT

= SV

DD

/2

PPC440SP

Note:

This diagram illustrates the model of the DDR SDRAM interface used when generating simulation timing data.

It is

not

a recommended physical circuit design for this interface. An actual interface design will depend on many

factors, including the type of memory used and the board layout.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC50505 | |

| PPC511 | |

| PPC603EFACT | MPC603e Host Processor Fact Sheet |

| PPC604EFACT | MPC604e Microprocessor Fact Sheet (discontinued) |

| PPD56-10 | Logic IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC-46 | 功能描述:電源變壓器 115/230Vac 50/60Hz 1.5VA RoHS:否 制造商:Triad Magnetics 功率額定值:12 VA 初級電壓額定值:115 V / 230 V 次級電壓額定值:12 V / 24 V 安裝風(fēng)格:SMD/SMT 一次繞組:Dual Primary Winding 二次繞組:Dual Secondary Winding 長度:2.5 in 寬度:2 in 高度:1.062 in |

| PPC460EX-NUA1000T | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 1.2 GHZ, 2 10/100/1G ETHERNET, US - Trays |

| PPC460EX-NUA1200T | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 1.2 GHZ, 2 10/100/1G ETHERNET, US - Trays |

| PPC460EX-NUA600T | 制造商:AppliedMicro 功能描述:MPU 460EX RISC 128-Bit 90nm 600MHz 1.8V/2.5V/3.3V 728-Pin TEBGA Tray 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 1.2 GHZ, 2 10/100/1G ETHERNET, US - Trays |

| PPC460EX-NUA800T | 制造商:AppliedMicro 功能描述:MPU 460EX RISC 128-Bit 90nm 800MHz 1.8V/2.5V/3.3V 728-Pin TEBGA Tray 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 1.2 GHZ, 2 10/100/1G ETHERNET, US - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。