- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378056 > PM73488 (PMC-SIERRA INC) 5 Gbit/s ATM Switch Fabric Element PDF資料下載

參數(shù)資料

| 型號: | PM73488 |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 5 Gbit/s ATM Switch Fabric Element |

| 中文描述: | ATM SWITCHING CIRCUIT, PBGA596 |

| 封裝: | EPBGA-596 |

| 文件頁數(shù): | 45/135頁 |

| 文件大小: | 1735K |

| 代理商: | PM73488 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁

PMC-Sierra, Inc.

PM73488 QSE

L

PMC-980616

Issue 3

5 Gbit/s ATMSwitch Fabric Element

Released

Datasheet

47

4

QSE FEATURE DESCRIPTIONS

4.1

The QSE has an algorithm that allows unicast cells to take advantage of multiple paths in multistage switch fabrics.

This algorithm is run simultaneously by all QSEs in a system. Since the position (row and column) of each QSE is

known (refer to

section 9.3.26 “SWITCH_FABRIC_ROW” on page 107

and to

section 9.3.27

“SWITCH_FABRIC_COLUMN” on page 108

), and they all receive a synchronizing strobe (CELL_24_START),

each QSE can determine exactly what the other QSEs are doing. This enables the QSEs to act globally to minimize

cell congestion in the switch fabric.

Distribution Algorithm

4.2

Each QSE needs to be informed when the window occurs during which the SE_SOC_IN is valid for the input ports.

Generally, since this window can vary from one QSE to another in the fabric, it is made software programmable by

setting the CELL_START_OFFSET register (refer to

section 9.3.28 “CELL_START_OFFSET” on page 109

). The

significance of this register is as follows: The QSE generates an internal signal called "Local CELL_START", which

is simply a delayed version of external CELL_START input, where the delay is the number of clock cycles given in

the CELL_START_OFFSET register. The valid window for accepting SE_SOC_IN is the 8-clock-cycle interval

immediately preceding the pulse of local CELL_START signal. (For a detailed timing diagram, see “Relation

Between External CELL_START and Local CELL_START” on page 47.)

Cell Start Offset Logic

4.2.1

Relation Between External CELL_START and Local CELL_START

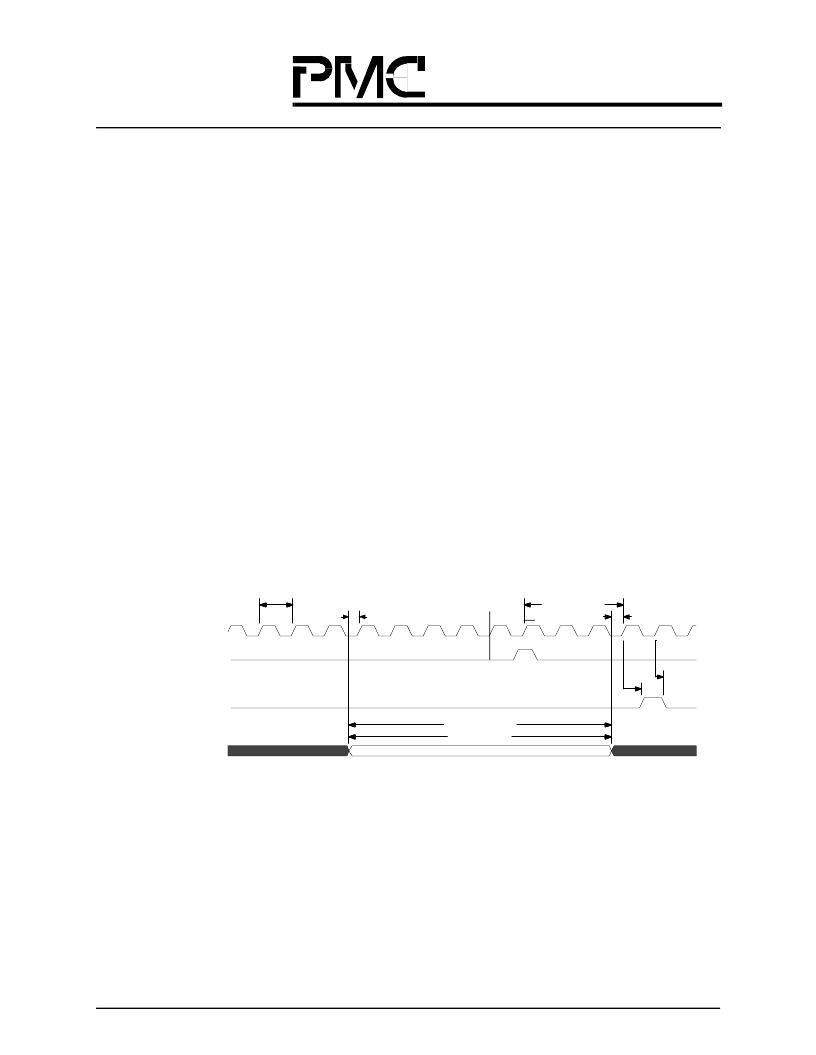

Figure 30 shows the relationship between the external CELL_START signal and the local CELL_START signal,

which is used internally by the QSE. The signal offset is programmable through the microprocessor interface (refer to

section 9.3.28 “CELL_START_OFFSET” on page 109

) to allow for easy system synchronization.

The QSE performs cut-through routing wherever possible and requires the SOC to be synchronized across all input

ports. For greater flexibility, the QSE allows cells starting within a window of eight clock pulses to be considered

valid. The end of the 8-clock-cycle window is also indicated by the local CELL_START signal.

Figure 30. QSE Cell-Level Timing

SOC Pulses Derived from the SE_SOC_IN Signals

Tseau

Tesu

CSTART Delay

CST High

8 Clock Cycles

Valid SOC Pulses

Clock Cycle

Delta

Delta

CST Low

SE_CLK

External CELL_START

Local CELL_START

SOC Pulses

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7349 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PM7350 | Dual Serial Link, PHY Multiplexer |

| PM7350-PI | DUAL SERIAL LINK PHY MULTIPLEXER |

| PM7351 | OCTAL SERIAL LINK MULTIPLEXER |

| PM7351-BI | OCTAL SERIAL LINK MULTIPLEXER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM73488PI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| PM73488-PI | 制造商:Rochester Electronics LLC 功能描述: 制造商:PMC-Sierra 功能描述: |

| PM7349 | 制造商:PMC 制造商全稱:PMC 功能描述:Quad J2, E3 and DS-3 Framer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。