- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT9074 (Mitel Networks Corporation) T1/E1/J1 Single Chip Transceiver(T1/E1/J1單片收發(fā)器) PDF資料下載

參數(shù)資料

| 型號(hào): | MT9074 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | T1/E1/J1 Single Chip Transceiver(T1/E1/J1單片收發(fā)器) |

| 中文描述: | T1/E1/J1收發(fā)單芯片收發(fā)器(T1/E1/J1收發(fā)單片收發(fā)器) |

| 文件頁(yè)數(shù): | 30/120頁(yè) |

| 文件大小: | 362K |

| 代理商: | MT9074 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

MT9074

Advance Information

30

channels from the write pointer, a slip will occur,

which will put the read pointer 28 channels from the

write pointer. This provides a worst case hysteresis

of 13 channels peak (26 channels peak-to-peak) or a

wander tolerance of 208 UI.

Framing Algorithm

Frame Alignment in T1 Mode

In T1 mode MT9074 will synchronize to DS1 lines

formatted with either the D4 or ESF protocol. In

either mode the framer maintains a running 3 bit

history of received data for each of the candidate bit

positions. Candidate bit positions whose incoming

patterns fail to match the predicted pattern (based on

the 3 bit history) are winnowed out. If, after a 10 bit

history has been examined, only one candidate bit

position remains within the framing bit period, the

receive side timebase is forced to align to that bit

position. If no candidates remain after a 10 bit

history, the process is re-initiated. If multiple

candidates exist after a 24 bit history timeout period,

the framer forces the receive side timebase to

synchronize to the next incoming valid candidate bit

position. In the event of a reframe, the framer starts

searching at the next bit position over. This prevents

persistent locking to a mimic as the controller may

initiate a software controlled reframe in the event of

locking to a mimic.

Under software control the framing criteria may be

tuned (see Framing Mode Select Register, page 1H,

address 10H). Selecting D4 framing invites a further

decision whether or not to include a cross check of

Fs bits along with the Ft bits. If Fs bits are checked

(by setting control bit CXC high - bit 5 of the Framing

Mode Select Word, page 1H, address 10H),

multiframer alignment is forced at the same time as

terminal frame alignment. If only Ft bits are checked,

multiframe alignment is forced separately, upon

detection of the Fs bit history of 00111 (for normal

D4 trunks) or 000111000111 (for SLC-96 trunks).

For D4 trunks, a reframe on the multiframe alignment

may be forced at any time without affecting terminal

frame alignment.

In ESF mode the circuit will optionally confirm the

CRC-6 bits before forcing a new frame alignment.

This is programmed by setting control bit CXC high

(bit 5 of the Framing Mode Select Word, page 1H,

address 10H). A CRC-6 confirmation adds a

minimum of 6 milliseconds to the reframe time. If no

CRC-6 match is found after 16 attempts, the framer

moves to the next valid candidate bit position

(assuming other bit positions contain a match to the

framing pattern) or re-initiates the whole framing

procedure (assuming no bit positions have been

found to match the framing pattern).

The framing circuit is off - line. During a reframe, the

rest of the circuit operates synchronous with the last

frame alignment. Until such time as a new frame

alignment is achieved, the signalling bits are frozen

in their states at the time that frame alignment was

lost, and error counting for Ft, Fs, ESF framing

pattern or CRC-6 bits is suspended.

Frame Alignment in E1 mode

In E1 mode MT9074 contains three distinct framing

algorithms:

basic

frame

multiframe

alignment

and

alignment. Figure 17 is a state diagram that

illustrates these algorithms and how they interact.

alignment,

CRC-4

signalling

multiframe

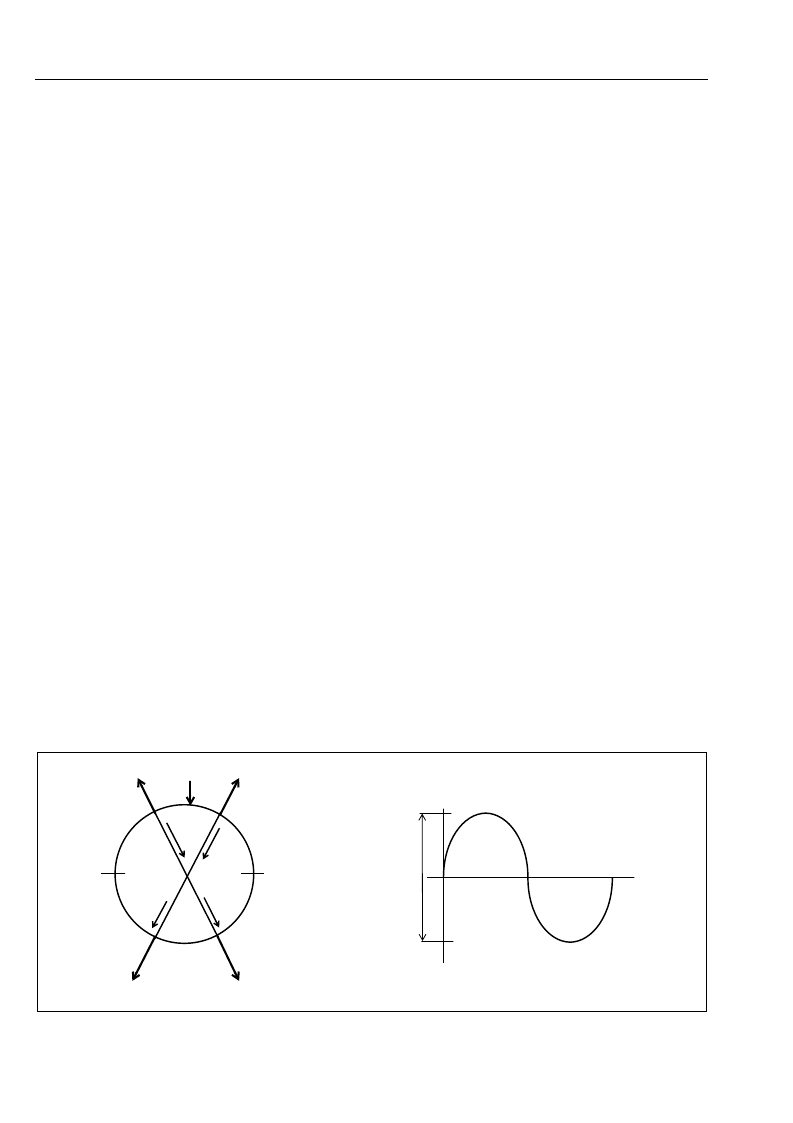

Figure 14 - Read and Write Pointers in the Slip Buffers

Write Pointer

60 CH

2 CH

47 CH

15 CH

34 CH

28 CH

512 Bit

Elastic

Store

13 CH

-13 CH

Wander Tolerance

Read Pointer

Read Pointer

Read Pointer

Read Pointer

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9075B | E1 Single Chip Transceiver |

| MT9075B | E1 Single Chip Transceiver(E1單片收發(fā)器) |

| MT9075 | E1 Single Chip Transceiver |

| MT9075A | E1 Single Chip Transceiver |

| MT9075AL | E1 Single Chip Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9074_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 Single Chip Transceiver |

| MT9074AL | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AL1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AP | 制造商:Microsemi Corporation 功能描述: |

| MT9074AP1 | 制造商:Microsemi Corporation 功能描述:T1/E1/J1 SGLE CHIP XSCR 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 68PLCC - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TXRX SGL T1/E1 68PLCC 制造商:Microsemi Corporation 功能描述:IC TXRX SGL T1/E1 68PLCC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。