- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT9074 (Mitel Networks Corporation) T1/E1/J1 Single Chip Transceiver(T1/E1/J1單片收發(fā)器) PDF資料下載

參數(shù)資料

| 型號(hào): | MT9074 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | T1/E1/J1 Single Chip Transceiver(T1/E1/J1單片收發(fā)器) |

| 中文描述: | T1/E1/J1收發(fā)單芯片收發(fā)器(T1/E1/J1收發(fā)單片收發(fā)器) |

| 文件頁數(shù): | 29/120頁 |

| 文件大?。?/td> | 362K |

| 代理商: | MT9074 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

Advance Information

MT9074

29

system the receive data is in phase with the E1.5o

clock, the C4b clock is phase-locked to the E1.5o

clock, and the read and write positions of the slip

buffer will remain fixed with respect to each other.

In a multi-trunk slave or loop-timed system (i.e.,

PABX application) a single trunk will be chosen as a

network synchronizer, which will function as

described in the previous paragraph. The remaining

trunks will use the system timing derived from the

synchronizer to clock data out of their slip buffers.

Even though the PCM 30 signals from the network

are synchronous to each other, due to multiplexing,

transmission impairments and route diversity, these

signals may jitter or wander with respect to the

synchronizing trunk signal. Therefore, the E1.5o

clocks of non-synchronizer trunks may wander with

respect to the C1.50 clock of the synchronizer and

the system bus.

Network standards state that, within limits, trunk

interfaces must be able to receive error-free data in

the presence of jitter and wander (refer to network

requirements for jitter and wander tolerance). The

MT9074 will allow a maximum of 26 channels (208

UI, unit intervals) of wander and low frequency jitter

before a frame slip will occur.

The minimum delay through the receive slip buffer is

approximately two channels and the maximum delay

is approximately 60 channels (see Figure 14).

When the C4b and the E1.5o clocks are not phase-

locked, the rate at which data is being written into the

slip buffer from the PCM 30 side may differ from the

rate at which it is being read out onto the ST-BUS. If

this situation persists, the delay limits stated in the

previous paragraph will be violated and the slip

buffer will perform a controlled frame slip. That is, the

buffer pointers will be automatically adjusted so that

a full PCM 30 frame is either repeated or lost. All

frame slips occur on PCM 30 frame boundaries.

Two status bits, RSLIP and RSLPD (page03H,

address13H) give indication of a slip occurrence and

direction. RSLIP changes state in the event of a slip.

If RSLPD=0, the slip buffer has overflowed and a

frame was lost; if RSLPD=1, an underflow condition

occurred and a frame was repeated. A maskable

interrupt SLPI (page 01H, address 1BH) is also

provided.

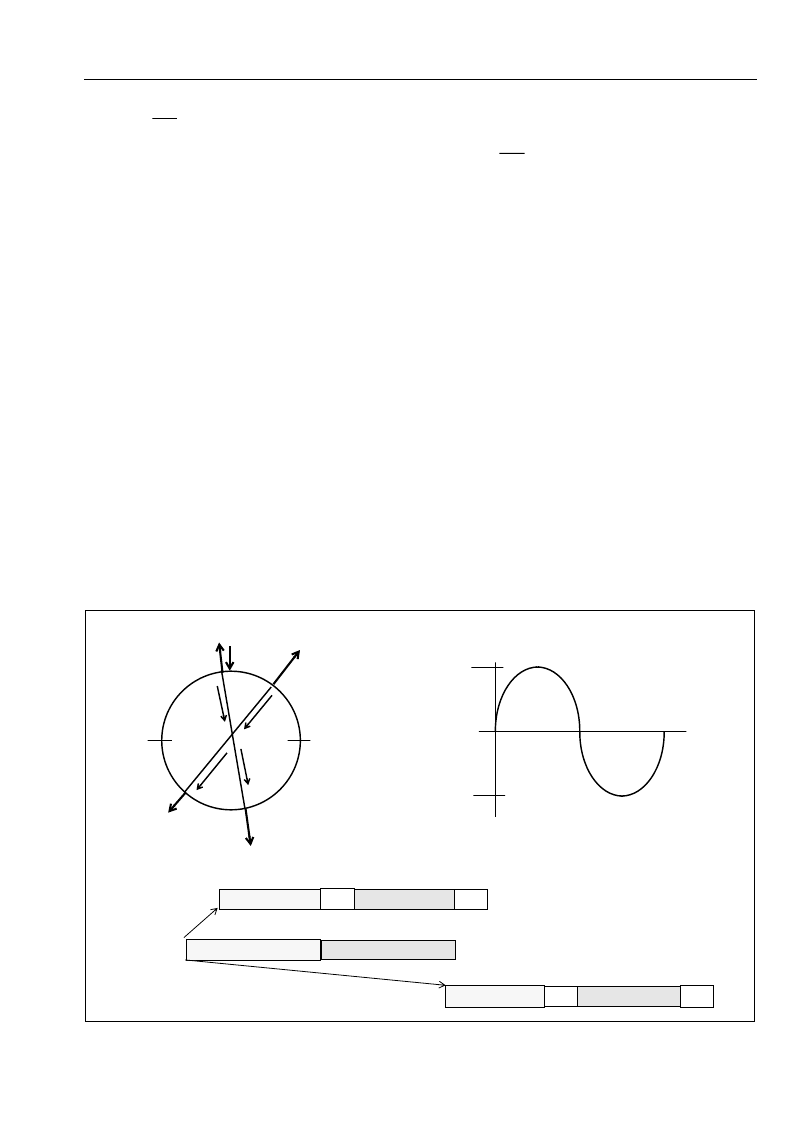

Figure 14 illustrates the relationship between the

read and write pointers of the receive slip buffer.

Measuring clockwise from the write pointer, if the

read pointer comes within two channels of the write

pointer a frame slip will occur, which will put the read

pointer 34 channels from the write pointer.

Conversely, if the read pointer moves more than 60

Figure 13 - Read and write pointers in the receive slip buffers

Write

Pointer

0 uS

249 uS

32 uS

188 uS

62 uS

157 uS

512 Bit

Elastic

Store

92 uS

92 uS

Wander Tolerance

Read Pointer

Read Pointer

Read Pointer

Read Pointer

Frame 0

Frame 1

Frame 0

Frame 1

Frame 0

Frame 1

XXX

XXX

XXX

XXX

Write Vectors

Read Vectors

Minimum Delay

Read Vectors - Maximum Delay

124 uS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9075B | E1 Single Chip Transceiver |

| MT9075B | E1 Single Chip Transceiver(E1單片收發(fā)器) |

| MT9075 | E1 Single Chip Transceiver |

| MT9075A | E1 Single Chip Transceiver |

| MT9075AL | E1 Single Chip Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9074_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 Single Chip Transceiver |

| MT9074AL | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AL1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AP | 制造商:Microsemi Corporation 功能描述: |

| MT9074AP1 | 制造商:Microsemi Corporation 功能描述:T1/E1/J1 SGLE CHIP XSCR 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 68PLCC - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TXRX SGL T1/E1 68PLCC 制造商:Microsemi Corporation 功能描述:IC TXRX SGL T1/E1 68PLCC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。