- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT9074 (Mitel Networks Corporation) T1/E1/J1 Single Chip Transceiver(T1/E1/J1單片收發(fā)器) PDF資料下載

參數(shù)資料

| 型號(hào): | MT9074 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | T1/E1/J1 Single Chip Transceiver(T1/E1/J1單片收發(fā)器) |

| 中文描述: | T1/E1/J1收發(fā)單芯片收發(fā)器(T1/E1/J1收發(fā)單片收發(fā)器) |

| 文件頁數(shù): | 14/120頁 |

| 文件大?。?/td> | 362K |

| 代理商: | MT9074 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

MT9074

Advance Information

14

appropriate mode and Jitter attenuation capability of

the MT9074

The Digital Interface

T1 Digital Interface

In T1 mode DS1 frames are 193 bits long and are

transmitted at a frame repetition rate of 8000 Hz,

which results in an aggregate bit rate of 193 bits x

8000/sec= 1.544 Mbits/sec. The actual bit rate is

1.544 Mbits/sec +/-50 ppm optionally encoded in

B8ZS format. The Zero Suppression control register

(page 1, address 15H,) selects either B8ZS

encoding, forced one stuffing or alternate mark

inversion (AMI) encoding. Basic frames are divided

into 24 time slots numbered 1 to 24. Each time slot is

8 bits in length and is transmitted most significant bit

first (numbered bit 1). This results in a single time

slot data rate of 8 bits x 8000/sec. = 64 kbits/sec.

It should be noted that the Mitel ST-BUS has 32

channels numbered 0 to 31. When mapping to the

DS1 payload only the first 24 time slots and the last

(time slot 31, for the overhead bit) of an ST-BUS are

used (see Table 6). All unused channels are tristate.

When signalling information is written to the MT9074

in T1 mode using ST-BUS control links (as opposed

to direct writes by the microport to the on - board

signaling

registers),

corresponding to the selected DSTi channels

streams are used to transmit the signalling bits.

the

CSTi

channels

Since the maximum number of signalling bits

associated with any channel is 4 (in the case of

ABCD), only half a CSTi channel is required for

sourcing the signaling bits. The choice of which half

of the channel to use is selected by the control bit

MSN (page 01H address 14H). The same control bit

selects which half of the CSTo channel will contain

receive signaling information (the other nibble in the

channel being tristate). Unused channels are tristate.

The most significant bit of an eight bit ST-BUS

channel is numbered bit 7 (see Mitel Application

Note MSAN-126). Therefore, ST-BUS bit 7 is

synonymous with DS1 bit 1; bit 6 with bit 2: and so

on.

Frame and Superframe Structure in T1 mode

Multiframing

In T1 mode, DS1 trunks contain 24 bytes of serial

voice/data channels bundled with an overhead bit.

The frame overhead bit contains a fixed repeating

pattern used to enable DS1 receivers to delineate

frame boundaries. Overhead bits are inserted once

per frame at the beginning of the transmit frame

boundary. The DS1 frames are further grouped in

bundles of frames, generally 12 (for D4 applications)

or 24 frames (for ESF - extended superframe

applications) deep. Table 7 and 8 illustrate the D4

and ESF frame structures respectively.

For D4 links the frame structure contains an

alternating 101010... pattern inserted into every

second overhead bit position. These bits are

intended for determination of frame boundaries, and

they are referred to as Ft bits. A separate fixed

pattern, repeating every superframe, is interleaved

with the Ft bits. This fixed pattern (001110), is used

to delineate the 12 frame superframe. These bits are

referred to as the Fs bits. In D4 frames # 6 and #12,

the LSB of each channel byte may be replaced with

A bit (frame #6) and B bit (frame #12) signalling

information.

For ESF links the 6 bit framing pattern 001011,

inserted into every 4th overhead bit position, is used

to delineate both frame and superframe boundaries.

Frames #6, 12, 18 and 24 contain the A, B, C and D

signalling bits, respectively. A 4 kHz data link is

embedded in the overhead bit position, interleaved

between the framing pattern sequence (FPS) and the

transmit CRC-6 remainder (from the calculation done

on the previous superframe), see Table 8.

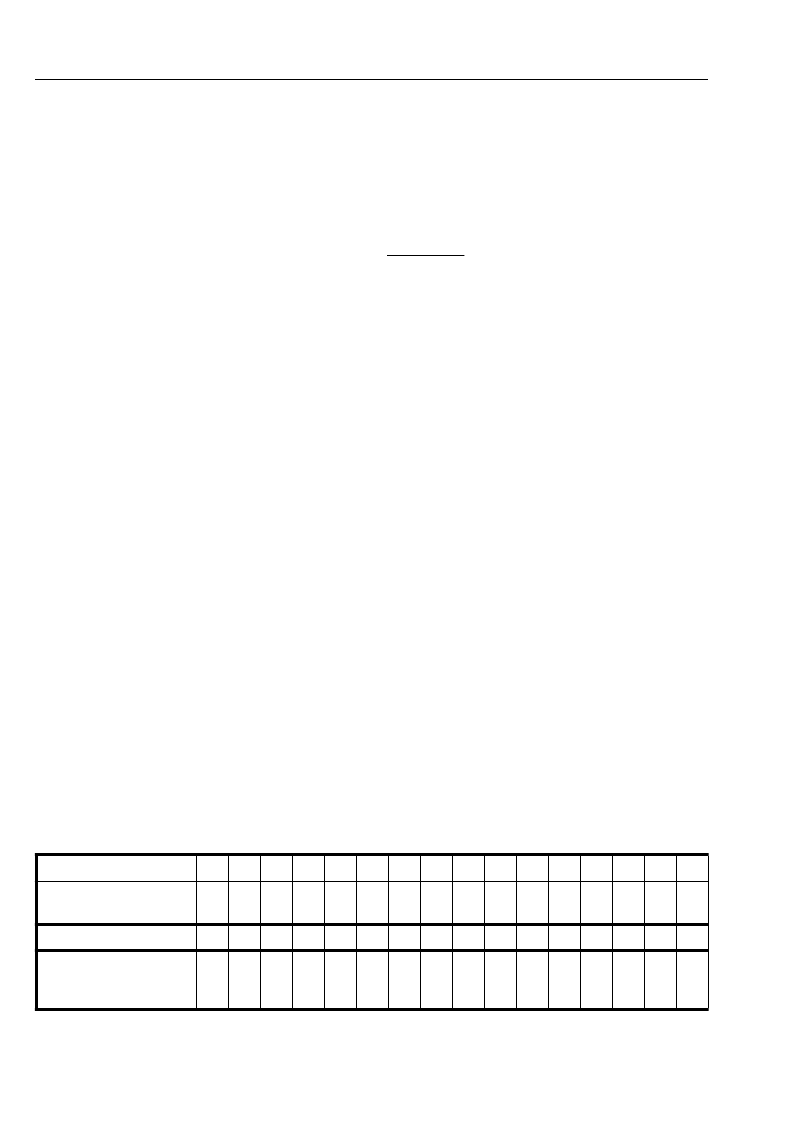

DS1 Timeslots

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Voice/Data Channels

(DSTi/o and CSTi/o)

0

1

2

3

4

5

6

7

7

9

10

11

12

13

14

15

Ds1 Timeslots

17

18

19

20

21

22

23

24

-

-

-

-

-

-

-

-

Voice/Data Channels

(DSTi/o and CSTi/o)

16

17

18

19

20

21

22

23

24

x

25

x

26

x

27

x

28

x

29

x

30

x

31

S

bit

Table 6 - STBUS vs. DS1 to Channel Relationship(T1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9075B | E1 Single Chip Transceiver |

| MT9075B | E1 Single Chip Transceiver(E1單片收發(fā)器) |

| MT9075 | E1 Single Chip Transceiver |

| MT9075A | E1 Single Chip Transceiver |

| MT9075AL | E1 Single Chip Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9074_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 Single Chip Transceiver |

| MT9074AL | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AL1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AP | 制造商:Microsemi Corporation 功能描述: |

| MT9074AP1 | 制造商:Microsemi Corporation 功能描述:T1/E1/J1 SGLE CHIP XSCR 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 68PLCC - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TXRX SGL T1/E1 68PLCC 制造商:Microsemi Corporation 功能描述:IC TXRX SGL T1/E1 68PLCC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。