- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299522 > MT48LC8M16A2BB-6ALIT:G 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA60 PDF資料下載

參數(shù)資料

| 型號: | MT48LC8M16A2BB-6ALIT:G |

| 元件分類: | DRAM |

| 英文描述: | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA60 |

| 封裝: | 8 X 16 MM, LEAD FREE, PLASTIC, FBGA-60 |

| 文件頁數(shù): | 28/57頁 |

| 文件大小: | 1506K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

34

PDF: 09005aef8091e66d/Source: 09005aef8091e625

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128MSDRAM.pmd – Rev. J; Pub. 1/05

2001 Micron Technology, Inc. All rights reserved.

128Mb: x4, x8, x16

SDRAM

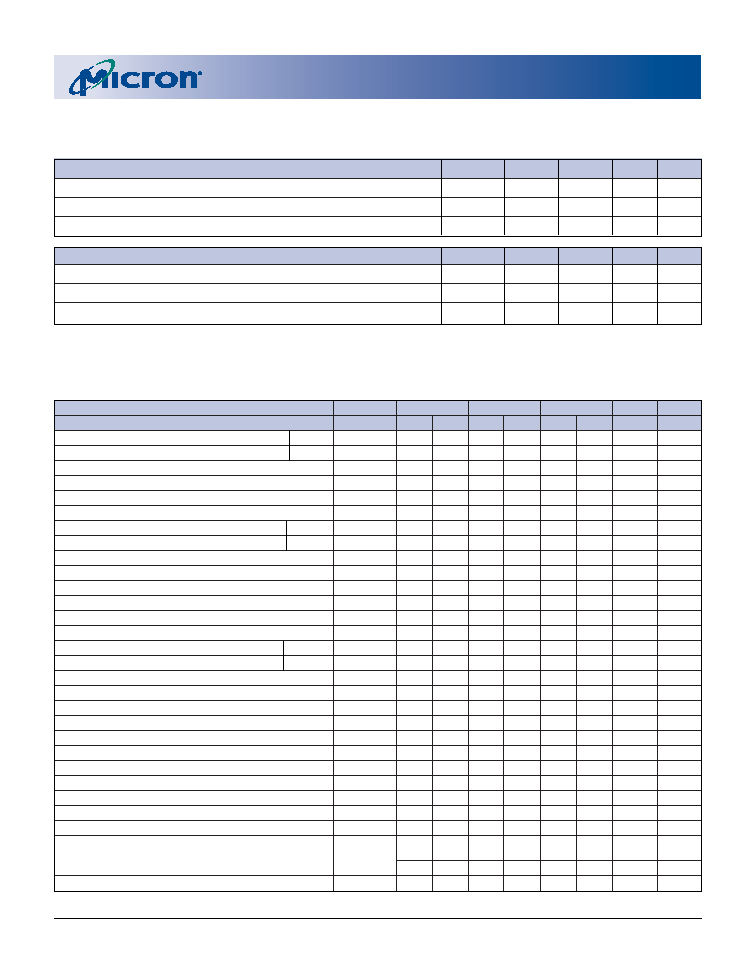

ELECTRICAL CHARACTERISTICS AND RECOMMENDED

AC OPERATING CONDITIONS

(Notes: 5, 6, 8, 9, 11; notes appear on page 36)

AC CHARACTERISTICS

-6A

-7E

-75

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

MIN

MAX

UNITS NOTES

Access time from CLK (pos. edge)

CL = 3

tAC(3)

5.4

ns

27

CL = 2

tAC(2)

5.4

6

ns

Address hold time

tAH

0.8

ns

Address setup time

tAS

1.5

ns

CLK high-level width

tCH

2.5

ns

CLK low-level width

tCL

2.5

ns

Clock cycle time

CL = 3

tCK(3)

6

7

7.5

ns

23

CL = 2

tCK(2)

-

7.5

10

ns

23

CKE hold time

tCKH

0.8

ns

CKE setup time

tCKS

1.5

ns

CS#, RAS#, CAS#, WE#, DQM hold time

tCMH

0.8

ns

CS#, RAS#, CAS#, WE#, DQM setup time

tCMS

1.5

ns

Data-in hold time

tDH

0.8

ns

Data-in setup time

tDS

1.5

ns

Data-out high-impedance time

CL = 3

tHZ(3)

5.4

ns

10

CL = 2

tHZ(2)

5.4

6

ns

10

Data-out low-impedance time

tLZ

111

ns

Data-out hold time (load)

tOH

333

ns

Data-out hold time (no load)

tOHN

1.8

ns

28

ACTIVE to PRECHARGE command

tRAS

42

120,000

37

120,000

44

120,000

ns

ACTIVE to ACTIVE command period

tRC

60

66

ns

ACTIVE to READ or WRITE delay

tRCD

18

15

20

ns

Refresh period (4,096 rows)

tREF

64

ms

AUTO REFRESH period

tRFC

60

66

ns

PRECHARGEcommandperiod

tRP

18

15

20

ns

ACTIVE bank a to ACTIVE bank b command

tRRD

12

14

15

ns

Transition time

tT

0.3

1.2

0.3

1.2

0.3

1.2

ns

7

WRITE recovery time

tWR

1 CLK +

–

24

7ns

7.5ns

12

14

15

ns

25

Exit SELF REFRESH to ACTIVE command

tXSR

67

75

ns

20

CAPACITANCE

(Note: 2; notes appear on page 36)

PARAMETER - TSOP “TG” Package

SYMBOL

MIN

MAX

UNITS NOTES

Input Capacitance: CLK

CI1

2.5

3.5

pF

29

Input Capacitance: All other input-only pins

CI2

2.5

3.8

pF

30

Input/Output Capacitance: DQs

CIO

4.0

6.0

pF

31

PARAMETER - FBGA “FB” Package

SYMBOL

MIN

MAX

UNITS NOTES

Input Capacitance: CLK

CI1

1.5

3.5

pF

34

Input Capacitance: All other input-only pins

CI2

1.5

3.8

pF

35

Input/Output Capacitance: DQs

CIO

3.0

6.0

pF

36

相關PDF資料 |

PDF描述 |

|---|---|

| MT49H8M36HU-33 | 8M X 36 DDR DRAM, 0.3 ns, PBGA144 |

| MT4C1024DJ-6L | 1M X 1 FAST PAGE DRAM, 60 ns, PDSO20 |

| MT4C2M8A1DJ-7STR | 2M X 8 FAST PAGE DRAM, 70 ns, PDSO28 |

| MT4LC1M16C5TG-8S | 1M X 16 FAST PAGE DRAM, 80 ns, PDSO44 |

| MT4LC2M8A1DJ-6TR | 2M X 8 FAST PAGE DRAM, 60 ns, PDSO28 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|

發(fā)布緊急采購,3分鐘左右您將得到回復。