- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN8187 (SMSC Corporation) High-Performance MII and RMII 10/100 Ethernet PHY with HP Auto-MDIX PDF資料下載

參數(shù)資料

| 型號: | LAN8187 |

| 廠商: | SMSC Corporation |

| 英文描述: | High-Performance MII and RMII 10/100 Ethernet PHY with HP Auto-MDIX |

| 中文描述: | 高性能信息產(chǎn)業(yè)部及RMII 10/100以太網(wǎng)PHY與HP Auto - MDIX功能 |

| 文件頁數(shù): | 32/66頁 |

| 文件大小: | 545K |

| 代理商: | LAN8187 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

High-Performance MII and RMII 10/100 Ethernet PHY with HP Auto-MDIX

Datasheet

Revision 0.6 (02-24-06)

32

SMSC LAN8187/LAN8187I

DATASHEET

4.12.1

Boot Strapping Configuration.

Due to a lower I/O voltage, a lower strapping resistor needs to be used to ensure the strapped

configuration is latched into the PHY device at power-on reset.

Note:

For VDDIO operation below +2.5V, SMSC recommends designs add external strapping

resistors in addition the internal strapping resistors to ensure proper strapped operation.

4.12.2

I/O Voltage Stability

The I/O voltage the System Designer applies on VDDIO needs to maintain its value with a tolerance

of +/- 10%. Varying the voltage up or down, after the PHY has completed power-on reset can cause

errors in the PHY operation.

4.13

PHY Management Control

The Management Control module includes 3 blocks:

Serial Management Interface (SMI)

Management Registers Set

Interrupt

4.13.1

Serial Management Interface (SMI)

The Serial Management Interface is used to control the LAN8187/LAN8187I and obtain its status. This

interface supports registers 0 through 6 as required by Clause 22 of the 802.3 standard, as well as

“vendor-specific” registers 16 to 31 allowed by the specification. Non-supported registers (7 to 15) will

be read as hexadecimal “FFFF”.

At the system level there are 2 signals, MDIO and MDC where MDIO is bi-directional open-drain and

MDC is the clock.

A special feature (enabled by register 17 bit 3) forces the PHY to disregard the PHY-Address in the

SMI packet causing the PHY to respond to any address. This feature is useful in multi-PHY

applications and in production testing, where the same register can be written in all the PHYs using a

single write transaction.

The MDC signal is an aperiodic clock provided by the station management controller (SMC). The MDIO

signal receives serial data (commands) from the controller SMC, and sends serial data (status) to the

SMC. The minimum time between edges of the MDC is 160 ns. There is no maximum time between

edges.

The minimum cycle time (time between two consecutive rising or two consecutive falling edges) is 400

ns. These modest timing requirements allow this interface to be easily driven by the I/O port of a

microcontroller.

The data on the MDIO line is latched on the rising edge of the MDC. The frame structure and timing

of the data is shown in

Figure 4.6

and

Figure 4.7

.

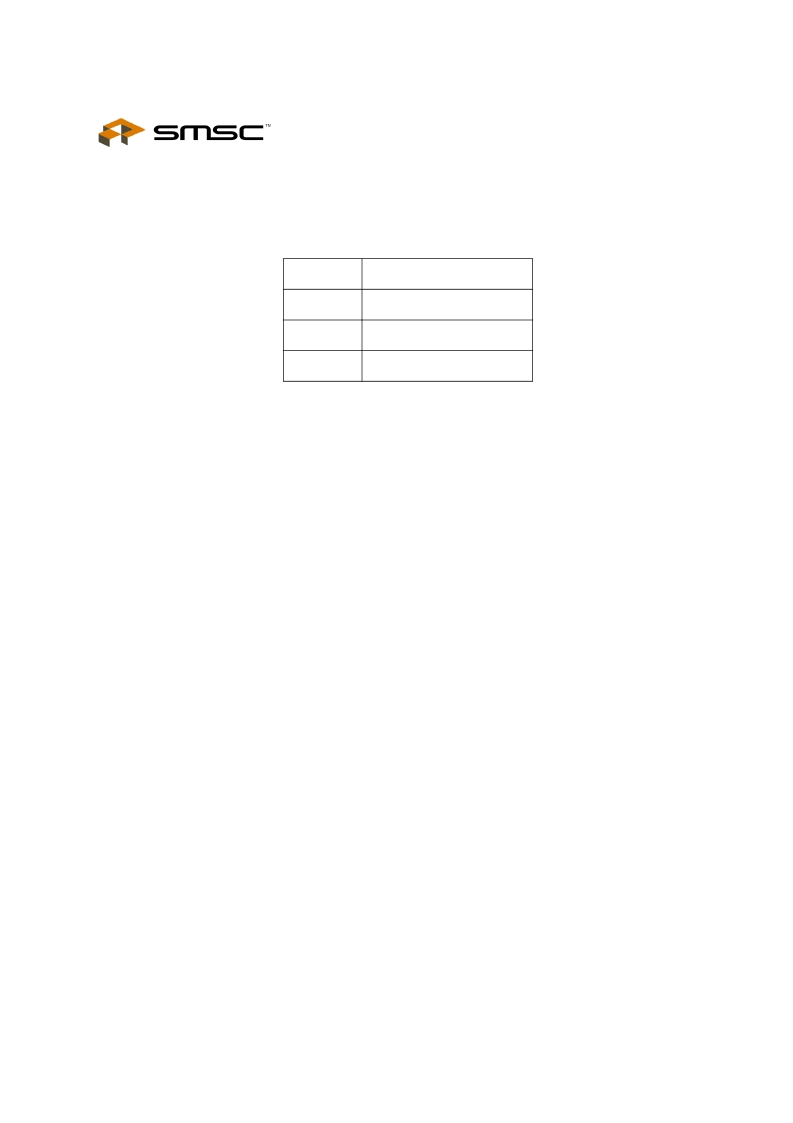

Table 4.3 Boot Strapping Configuration Resistors

I/O voltage

Pull-up/Pull-down Resistor

3.0 to 3.6

10k ohm resistor

2.0 to 3.0

7.5k ohm resistor

1.6 to 2.0

5k ohm resistor

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN83C175 | Ethernet CARDBUS Integrated Controller With Modem Support |

| LAN83C180 | 10/100 FAST ETHERNET PHY TRANSCEIVER |

| LAN83C185 | HIGH PERFORMANCE SINGLE CHIP LOW POWER 10/100 ETHERNET PHYSICAL LAYER TRANSCEIVER |

| LAN83C183-JD | FAST ETHERNET PHYSICAL LAYER DEVICE |

| LAN83C180TQFP | 10/100 FAST ETHERNET PHY TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN8187_06 | 制造商:SMSC 制造商全稱:SMSC 功能描述:【15kV ESD Protected MII/RMII Fast-Ethernet PHY with HP Auto-MDIX and SMSC flexPWRTM |

| LAN8187I | 制造商:SMSC 制造商全稱:SMSC 功能描述:High-Performance MII and RMII 10/100 Ethernet PHY with HP Auto-MDIX |

| LAN8187I-JT | 功能描述:以太網(wǎng) IC HiPerfrm Ethrnt PHY RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN8187-JT | 功能描述:以太網(wǎng) IC HiPerfrm Ethrnt PHY RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN83C171 | 制造商:SMSC 制造商全稱:SMSC 功能描述:EPIC/XF ACPI/PC 97 Compliant Integrated PCI 10/100 Mbps Fast Ethernet Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。