- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377549 > IS42S16128-10T (INTEGRATED SILICON SOLUTION INC) 128K Words x 16 Bits x 2 Banks (4-MBIT) SYNCHRONOUS DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號: | IS42S16128-10T |

| 廠商: | INTEGRATED SILICON SOLUTION INC |

| 元件分類: | DRAM |

| 英文描述: | 128K Words x 16 Bits x 2 Banks (4-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 中文描述: | 256K X 16 SYNCHRONOUS DRAM, 10 ns, PDSO50 |

| 封裝: | 0.400 INCH, TSOP2-50 |

| 文件頁數(shù): | 33/75頁 |

| 文件大?。?/td> | 638K |

| 代理商: | IS42S16128-10T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁

IS42S16128

ISSI

Integrated Silicon Solution, Inc. — 1-800-379-4774

Rev. A

03/13/00

33

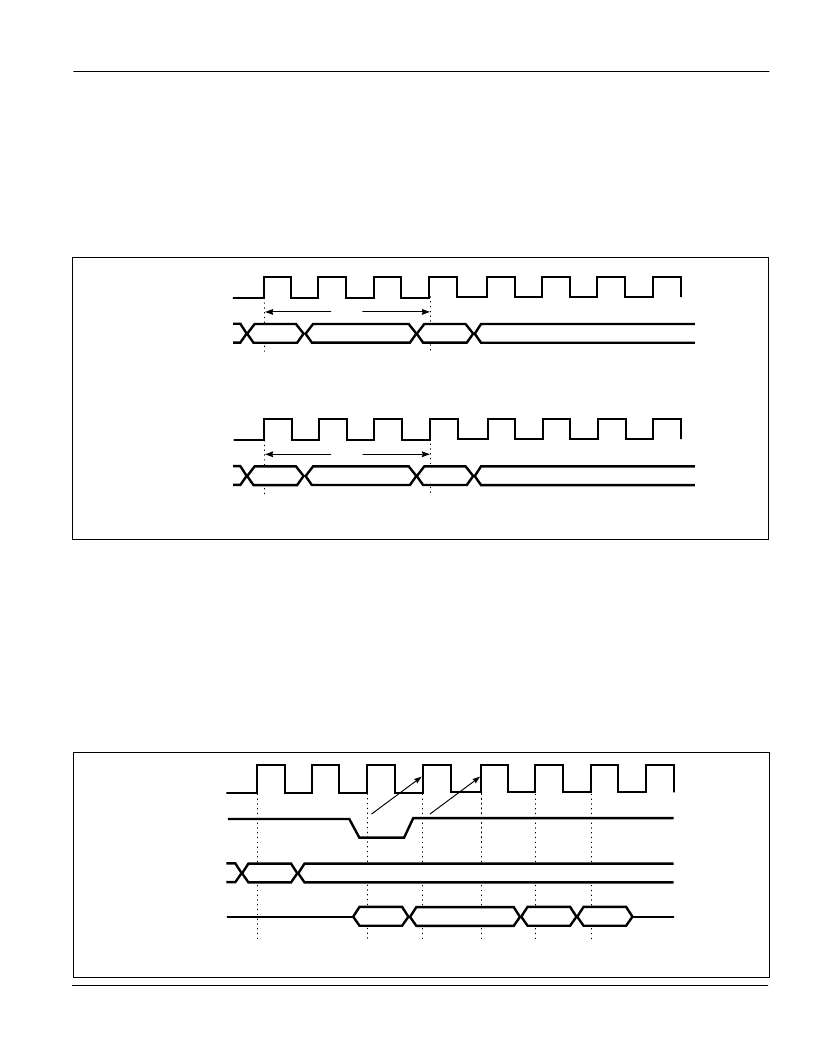

Bank Active Command Interval

When the selected bank is precharged, the period trp has

elapsed and the bank has entered the idle state, the bank

can be activated by executing the active command. If the

other bank is in the idle state at that time, the active

command can be executed for that bank after the period

t

RRD

has elapsed. At that point both banks will be in the

active state. When a bank active command has been

executed, a precharge command must be executed for

that bank within the ACT to PRE command period (t

RAS

max.). Also note that a precharge command cannot be

executed for an active bank before t

RAS

(min.) has elapsed.

After a bank active command has been executed and the

trcd period has elapsed, read write (including auto-

precharge) commands can be executed for that bank.

CAS

latency = 3

Clock Suspend

When the CKE pin is dropped from HIGH to LOW during

a read or write cycle, the IS42S16128 enters clock sus-

pend mode on the next CLK rising edge. This command

reduces the device power dissipation by stopping the

device internal clock. Clock suspend mode continues as

long as the CKE pin remains low. In this state, all inputs

other than CKE pin are invalid and no other commands

can be executed. Also, the device internal states are

maintained. When the CKE pin goes from LOW to HIGH,

CAS

latency = 2, burst length = 4

ACT 0

ACT 1

COMMAND

CLK

BANK ACTIVE (BANK 0)

BANK ACTIVE (BANK 1)

t

RRD

ACT 0

READ 0

COMMAND

CLK

BANK ACTIVE (BANK 0)

BANK ACTIVE (BANK 0)

t

RCD

clock suspend mode is terminated on the next CLK rising

edge and device operation resumes.

The next command cannot be executed until the recovery

period (tcka) has elapsed.

Since this command differs from the self-refresh command

described previously in that the refresh operation is not

performed automatically internally, the refresh operation

must be performed within the refresh period (tref). Thus the

maximum time that clock suspend mode can be held is just

under the refresh cycle time.

READ 0

COMMAND

CKE

I/O

CLK

D

OUT

0

D

OUT

1

D

OUT

2

D

OUT

3

READ (BANK 0)

CLOCK SUSPEND

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS42S16128-12T | 128K Words x 16 Bits x 2 Banks (4-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16128-8T | Chassis Mount and Din Rail Filters RoHS Compliant: Yes |

| IS42S16160B-7TL | 32Meg x 8, 16Meg x16 256-MBIT SYNCHRONOUS DRAM |

| IS42S16160B-7TLI | 32Meg x 8, 16Meg x16 256-MBIT SYNCHRONOUS DRAM |

| IS42S83200B | 32Meg x 8, 16Meg x16 256-MBIT SYNCHRONOUS DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS42S16128-12T | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:128K Words x 16 Bits x 2 Banks (4-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16128-8T | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:128K Words x 16 Bits x 2 Banks (4-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16160A-6T | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:256 Mb Synchronous DRAM |

| IS42S16160A-6TL | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:256 Mb Synchronous DRAM |

| IS42S16160A-7T | 制造商:Integrated Silicon Solution Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。