- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383075 > HSP50214BVI (HARRIS SEMICONDUCTOR) Programmable Downconverter PDF資料下載

參數(shù)資料

| 型號(hào): | HSP50214BVI |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類(lèi): | 通信及網(wǎng)絡(luò) |

| 英文描述: | Programmable Downconverter |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP120 |

| 文件頁(yè)數(shù): | 13/60頁(yè) |

| 文件大小: | 573K |

| 代理商: | HSP50214BVI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

3-13

The integration period counter can be set up to run

continuously or to count down and stop. Continuous integration

counter operation lets the counter run, with sampling occurring

every time the counter reaches zero. Because the processor

samples the detector read port asynchronous to the CLKIN,

data can be missed unless the status bit is monitored by the

processor to ensure that a sample is taken for every integration

count down sequence.

Additionally, in the HSP50214B, the ability to align the

start/restart of the input level detector integration period with

an external event is provided. This allows the sync signals,

which are synchronized to external events, to be used to align

all of the gain adjustments or measurements. If Control Word

27, Bit 17 is set to a logic one, the SYNCIN1 signal will cause

the input level detector to start/restart its integration period. If

Control Word 27, Bit 17 is set to a logic zero, control of the

start/restart of the input level detector integration period does

not respond to SYNCIN1.

In the count down and stop mode, the microprocessor read

commands can be synchronized to system events, such as the

start of a burst for a TDMA application. The integration counter

can be started at any time by writing to Control Word 2. At the

end of the integration period (counter = 0000), the upper 23 bits

of the accumulator are transferred to a holding register for

reading by the microprocessor. Note that it is not the restarting

of the counter (by writing to Control Word 2) that latches the

current value, but the end of the integration count. When the

accumulator results are latched, a bit is set in the Status

Register to notify the processor. Reading the most significant

byte of the 23 bits clears the status bit. See the Microprocessor

Read Section. Figure 11 illustrates a typical AGC detection

process.

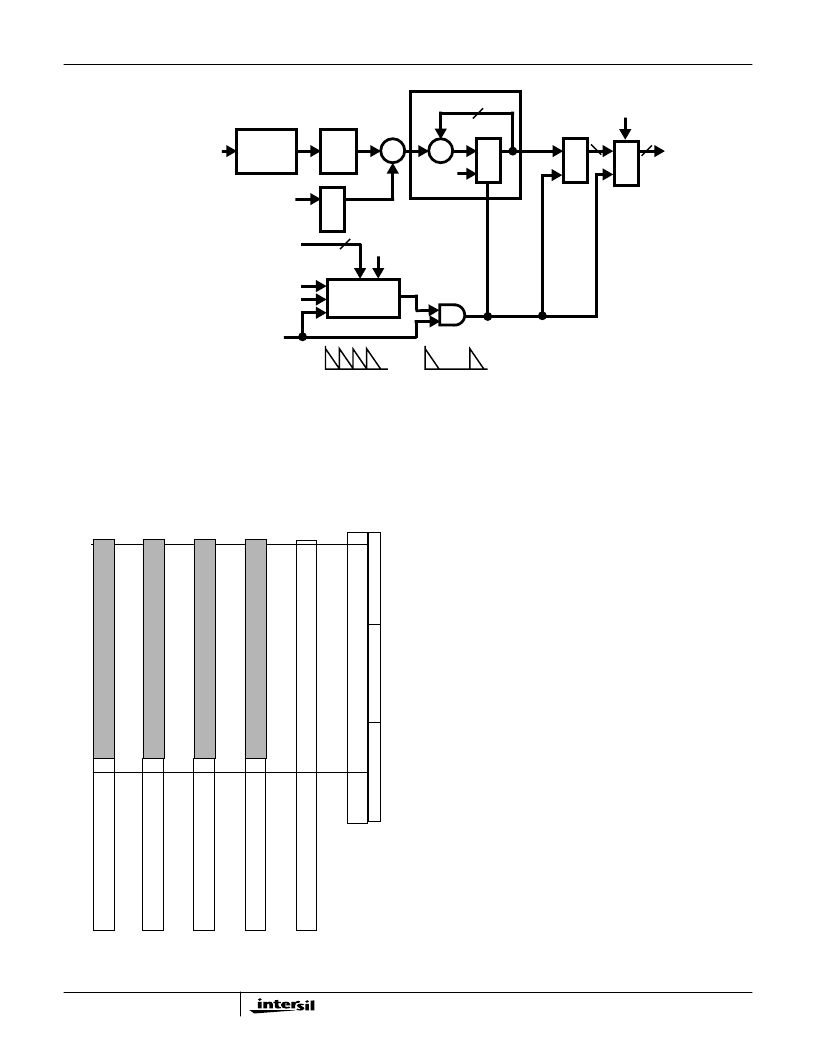

FIGURE 9.

INPUT

GATING

LOGIC

|X|

R

E

G

+

+

R

E

G

ACCUMULATOR

CLKIN

CLKIN

INPUT_THRESHOLD

INTEGRATION_INTERVAL

START

INTEGRATION_MODE

IN(13:0)

“0”

TO

μ

PROC

ADDR(2:0)

32

24

8

16

CONTINUOUS

SINGLE

R

E

G

M

U

X

COUNTER

Controlled via microprocessor interface.

A

O

I

M

T

μ

P

2

0

2

-1

2

-2

2

-3

2

-4

2

-5

2

-6

2

-7

2

-8

2

-9

2

-10

2

-11

2

-12

2

-13

0

2

-1

2

-2

2

-3

2

-4

2

-5

2

-6

2

-7

2

-8

2

-9

2

-10

2

-11

2

-12

2

-13

-2

0

2

-1

2

-2

2

-3

2

-4

2

-5

2

-6

2

-7

2

-8

2

-9

2

-10

2

-11

2

-12

2

-13

2

0

2

-1

2

-2

2

-3

2

-4

2

-5

2

-6

2

-7

2

-8

2

-9

2

-10

2

-11

2

-12

2

-13

2

0

2

-1

2

-2

2

-3

2

-4

2

-5

2

-6

2

-7

2

-8

2

-9

2

-10

2

-11

2

-12

2

-13

fS

-6dB

-12dB

-18dB

-24dB

-30dB

-36dB

-42dB

-48dB

-54dB

-60dB

-66dB

-72dB

-78dB

2

14

2

13

2

12

2

11

2

10

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

17

2

16

2

15

2

18

2

0

2

-1

2

-2

2

-3

2

-4

2

14

2

13

2

12

2

11

2

10

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

17

2

16

2

15

2

18

0

0

0

0

R

P

A

FIGURE 10. INPUT THRESHOLD DETECTOR BIT WEIGHTING

HSP50214B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT84 | ADSL Coupling Transformers |

| HT84-00594 | ADSL Coupling Transformers |

| HT8400594S | ADSL Coupling Transformers |

| HT84-00595 | ADSL Coupling Transformers |

| HT84-00596 | ADSL Coupling Transformers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50214BVIZ | 功能描述:上下轉(zhuǎn)換器 120L MQFP INDTEMP 14-BIT PROG DWNCNVRT RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PQFP-128 |

| HSP50214VC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP50214VI | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP50215 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:DSP Modulator Evaluation Board |

| HSP50215EVAL | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:DSP Modulator Evaluation Board |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。