- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371898 > HSP50016JC-75 (INTERSIL CORP) Digital Down Converter PDF資料下載

參數(shù)資料

| 型號: | HSP50016JC-75 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 數(shù)字信號處理外設 |

| 英文描述: | Digital Down Converter |

| 中文描述: | 16-BIT, DSP-MIXER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 27/31頁 |

| 文件大小: | 209K |

| 代理商: | HSP50016JC-75 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁

3-224

Let’s return to the clock calculation example found in the Output

Formatter, and add the requirement of 4 time slots. The

calculations in the Example Clock Calculation Section remain

true, but step 8 must be added:

8. Now lets consider the multichannel timing. Each channel

must output the data at no less than 1.725MHz to get all

the I/Q data out in the allocated time for the assigned time

slot. Time margin is created when the output is clocked out

at a higher rate. Because each channel is outputting data

in only one of four channels, the effective output rate for

each channel is 1.725MHz /4 = 431.25kHz, even though

the part is outputting data 1.7MHz in every time slot.

. . . . . . . . . . Effective Channel Output Rate = 431.25kHz

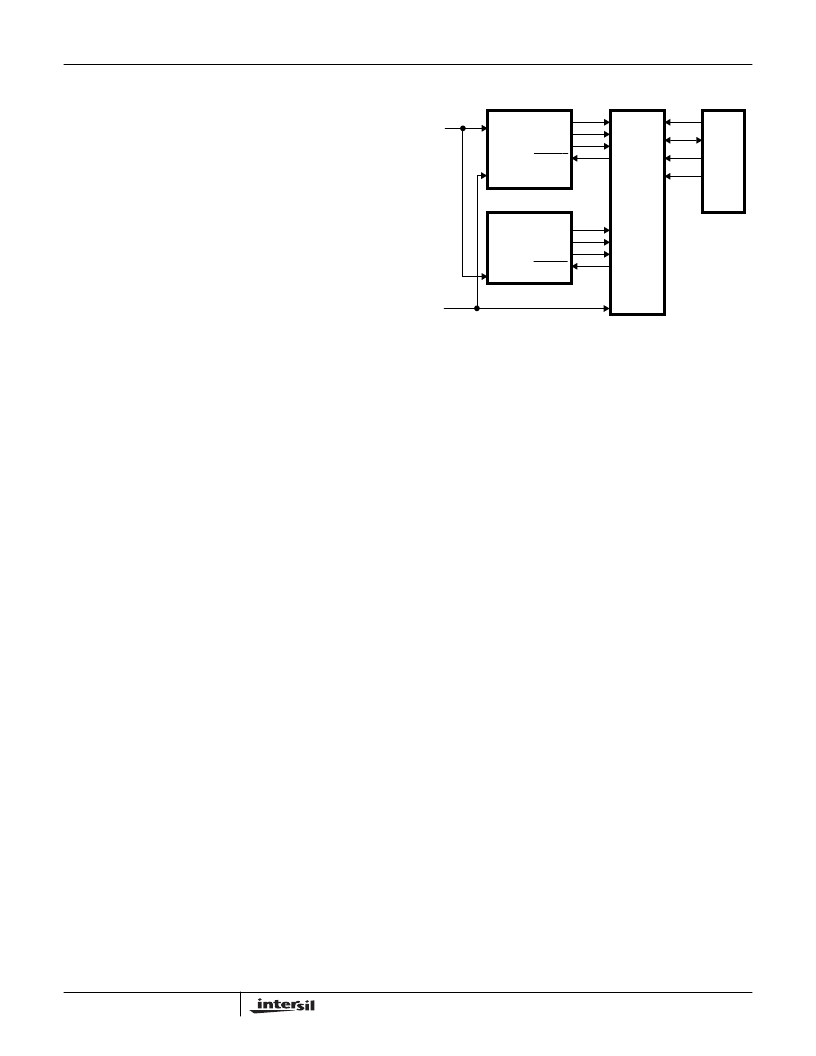

Alternatively, the processor can request data from each of

the DDCs asynchronously. In this setup, Requested Output

Mode is used. The Data Concentrator polls each channel

individually and is responsible for ensuring that each

channel is polled before the output data is lost. The Data

Concentrator is a custom circuit designed by the user. A

Block Diagram of such a system is shown in Figure 23. The

interface between the controller and the DDCs has been

omitted for the sake of clarity.

References

[1] Hogenauer, Eugene V., An Economical Class of Digital

Filters for Decimation and Interpolation, IEEE

Transactions on Acoustics, Speech and Signal

Processing, April 1981.

[2] IEEE Standard Test Access Port and Boundary-Scan

Architecture, IEEE Std 1149.1 - 1990.

HSP50016

I

IQCLK

IQSTB

IQSTRT

HSP50016

I

IQCLK

IQSTB

IQSTRT

A0-15

D0

DATA0-15

CLK

DATA0-15

CLK

DATA

FROM

A/D

SYSTEM

CLOCK

DATA

R/W

STRB

CONCENTRATOR

MICRO-

PROCESSOR

FIGURE 23. CIRCUIT FOR MULTIPLE CHANNEL OPERATION

(REQUESTED OUTPUT)

HSP50016

相關PDF資料 |

PDF描述 |

|---|---|

| HSP50110JC-60 | Communications Tuner Circuit |

| HSP50306SC-25 | Digital QPSK Demodulator |

| HSP50306SC-2596 | Digital QPSK Demodulator |

| HSP50306SC-27 | Digital QPSK Demodulator |

| HSP50306SC-2796 | Digital QPSK Demodulator |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50016JI-52 | 制造商:Rochester Electronics LLC 功能描述:DIGITAL DOWN CONVERTER 44 PLCC, 52MHZ, COMM,INDS - Bulk |

| HSP50016JM-5296R3571 | 制造商:Intersil Corporation 功能描述:ROCKWELL HSP50016JC-5296 W/BRAND,-55/+125C OP TEMP,ELECTR - Tape and Reel |

| HSP50016JM-52R3571 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP50110 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital Quadrature Tuner |

| HSP50110_01 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital Quadrature Tuner |

發(fā)布緊急采購,3分鐘左右您將得到回復。