- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371898 > HSP50306SC-25 (INTERSIL CORP) Digital QPSK Demodulator PDF資料下載

參數(shù)資料

| 型號(hào): | HSP50306SC-25 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Digital QPSK Demodulator |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁數(shù): | 1/8頁 |

| 文件大小: | 37K |

| 代理商: | HSP50306SC-25 |

8-272

February 1998

HSP50306

Digital QPSK Demodulator

Features

25.6MHz or 26.97MHz Clock Rates

Single Chip QPSK Demodulator with 10kHz Tracking

Loop

Square Root of Raised Cosine (

α

= 0.4) Matched

Filtering

2.048 MBPS Reconstructed Output Data Stream

Bit Synchronization with 3kHz Loop Bandwidth

Internal Equalization for Multipath Distortion

6-Bit Real Input: Digitized 10.7MHz or 2.1MHz IF

Level Detection for External IF AGC Loop

0.1s Acquisition Time

10

-9

BER

<116mA on +5.0V Supply

Applications

Cable Data Link Receivers

Cable Control Channel Receivers

Description

The HSP50306 is a 6-bit QPSK demodulator chip designed

for use in high signal to noise environments which have some

multipath distortion. The part recovers 2.048 MBPS data from

samples of a QPSK modulated 10.7MHz or 2.1MHz carrier.

The chip coherently demodulates the waveform, recovers

symbol timing, adaptively equalizes the signal to remove

multipath distortion, differentially decodes and multiplexes the

data decisions. 8-A lock signal is provided to indicate when

the tracking loops are locked and the data decisions are valid.

To optimize performance, a gain error feedback signal is

provided which can be filtered and used to close an I.F. AGC

loop around the A/D converter.

The QPSK demodulator derives all timing from CLKIN. The

chip divides this clock by 2 to provide the sample clock for the

external A/D converter. The -27 version operates at a clock

input of 26.97MHz and demodulates a 10.7MHz QPSK signal

to recover the 2048 KSPS data. The -25 version operates at a

clock input of 25.6MHz and demodulates a 2.1MHz QPSK

signal to recover the 2048 KSPS data. Variation from these

CLKIN frequencies will progressively degrade the receive

data rate, the receive IF, acquisition sweep rate, acquisition

sweep range and loop bandwidths as the deviation increases

from normal CLKIN. Details on the maximum allowable devia-

tion are found in the Input Characteristics section. The

HSP50306 processes 6-bit offset binary data. 4-bit data pro-

vides adequate performance for many applications.

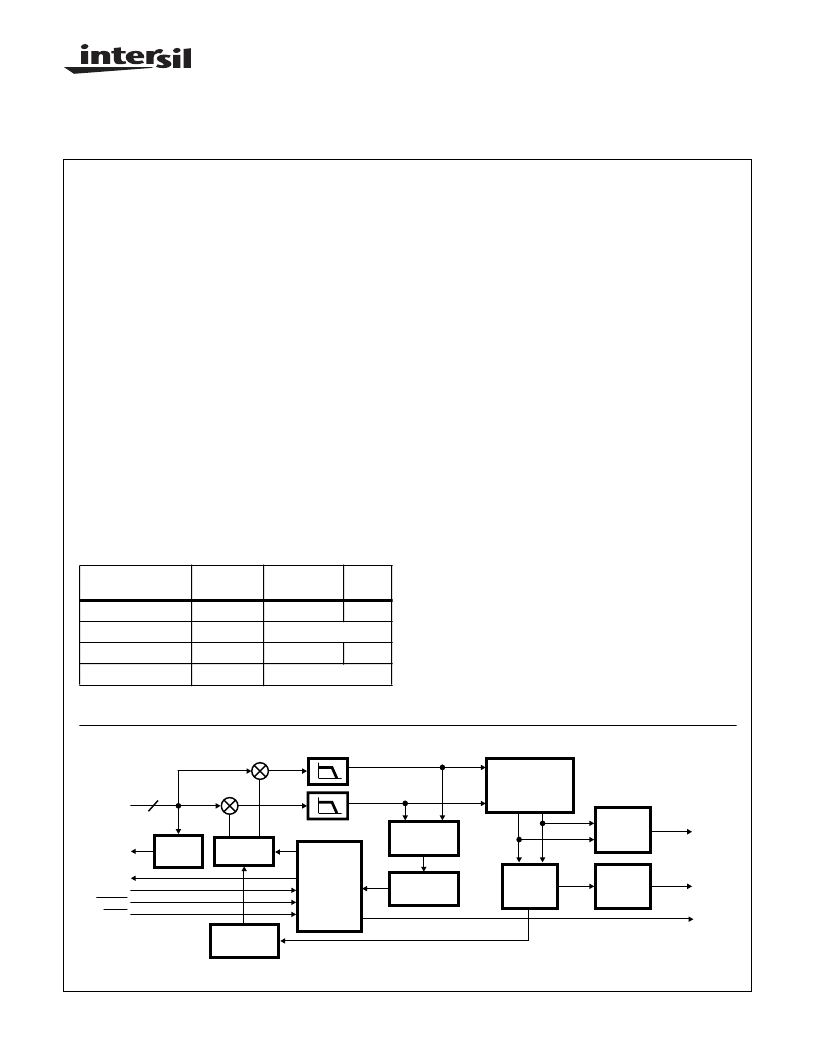

Block Diagram

Ordering Information

PART NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG.

NO.

HSP50306SC-27

0 to 70

16 Ld SOIC

M16.3

HSP50306SC-2796

0 to 70

Tape and Reel

HSP50306SC-25

0 to 70

16 Ld SOIC

M16.3

HSP50306SC-2596

0 to 70

Tape and Reel

NCO

SIN

COS

4 TAP

ADAPTIVE

EQUALIZER

BIT PHASE

DETECTOR

BIT SYNC

LOOP FILTER

TIMING

GENERATOR

CARRIER

PHASE

DETECT

DIFF.

DECODE/

MUX

CARRIER

LOOP FILTER

LOCK

DETECT

6

DIN0-5

AGCOUT

ADCLK

CLKIN

RESET

TEST

CLKOUT

DATAOUT

LOCK

I

Q

LEVEL

DETECT

I

Q

File Number

4162.2

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

Intersil Corporation 1999

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50306SC-2596 | Digital QPSK Demodulator |

| HSP50306SC-27 | Digital QPSK Demodulator |

| HSP50306SC-2796 | Digital QPSK Demodulator |

| HSP50306 | Digital QPSK Demodulator(數(shù)字QPSK解調(diào)器) |

| HSP9501JC-25 | Programmable Data Buffer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50306SC-2596 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital QPSK Demodulator |

| HSP50306SC-27 | 制造商:Rochester Electronics LLC 功能描述:QPSK DEMODULATOR 16 LEAD SOIC - Bulk |

| HSP50306SC-27 WAF | 制造商:Intersil Corporation 功能描述: |

| HSP50306SC-2796 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP50307 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Burst QPSK Modulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。