- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370213 > FMS988AKAC140 Signal Conditioner PDF資料下載

參數(shù)資料

| 型號(hào): | FMS988AKAC140 |

| 英文描述: | Signal Conditioner |

| 中文描述: | 信號(hào)調(diào)理 |

| 文件頁(yè)數(shù): | 27/29頁(yè) |

| 文件大小: | 481K |

| 代理商: | FMS988AKAC140 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)

FMS9875

PRODUCT SPECIFICATION

REV. 1.2.15 1/14/02

27

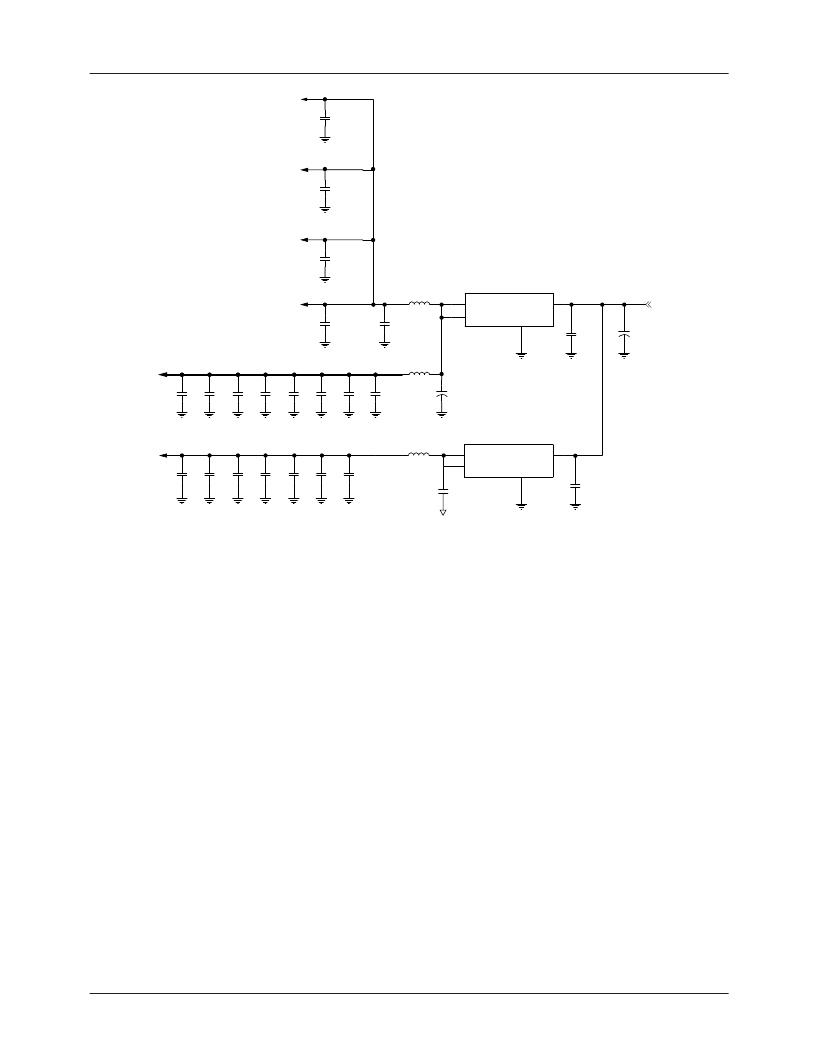

Figure 26. Recommended Power Distribution

VPLL

Power Input

Pin 39

Pin 37

Pin 33

Pins

26, 27

VADC Pins

VDD Pins

C4

0.1

μ

F

C5

10

μ

F

L1

BEAD

BEAD

BEAD

L2

L3

U1

RC1117-3.3

3

1

1

2

4

OUT

OUT

IN

ADJ/GND

OUT

OUT

IN

ADJ/GND

U2

RC1117-3.3

3

2

4

C3

0.01

μ

F

C2

0.1

μ

F

C1

0.01

μ

F

+

+

C24

10

μ

F

C25

10

μ

F

+

C7

10

μ

F

C23

0.1

μ

F

C6

0.1

μ

F

C8

0.1

μ

F

C9

0.1

μ

F

C10

0.1

μ

F

C11

0.1

μ

F

C12

0.1

μ

F

C13

0.1

μ

F

C14

0.1

μ

F

C15

0.1

μ

F

C16

0.1

μ

F

C17

0.1

μ

F

C18

0.1

μ

F

C19

0.1

μ

F

C20

0.1

μ

F

C21

0.1

μ

F

C22

0.1

μ

F

Physical placement of PLL power supply decoupling

components is critical. Bearing in mind the following

suggestions:

1.

All components should be placed in close proximity to

the FMS9875 pins.

2.

Routing through vias should be avoided, if possible.

3.

Each V

DDP

/GND pin pair: 26&27/28, 33/32, 37/38, and

39/40 should be decoupled with a either a 0.01 or 0.1 μF

capacitor (see Figure 24).

4.

Use Fair-rite 274 301 9447 bead.

Firmware

Best performance can be achieved by correctly setting the

FMS9875 registers. Here are some recommendations:

1.

For analog video, the sampling rate is usually 2X–3X

the video bandwidth. PLLN and PHASE are not critical.

For PC video, set the value of PLLN equal to the num-

ber of pixels to be sampled minus one. With this setting,

the number of samples per horizontal line equals the

number of pixels. If PLLN + 1 does not equal the num-

ber of pixels, there will be irregular intensities on text

and an interference pattern on a vertical grill pattern.

In the GBR mode, calibrate Offset and Gain by first set-

ting each input to 0mV. Then adjust OSGY, OSBP, and

OSRP to set each RGB data output D

7-0

= 0x00. Next

2.

3.

with 700mV input, adjust GGY, GBP and GRP so that

each RGB data output D

7-0

= (same value), typically

240 decimal. Average values during calibration to

minimize the impact of noise.

In the YP

B

P

R

mode, the Y-channel calibration procedure

is the same as for GBR. P

B

P

R

channels must be

calibrated differently. If the internal mid-scale clamp is

used, Offset is automatically preset. Only the Gain need

be adjusted to accomodate the swing from peak blue to

peak orange on the P

B

channel; and peak red to peak

cyan onthe P

R

channel. Average values during calibra-

tion to minimize the impact of noise.

Clamp registers, CD and CW, should be programmed to

maximize the period of the clamp during the backporch,

while not encroaching into the sync or active video

periods.

PHASE must be trimmed to minimize onscreen snow

(intensity noise) when a vertical grill pattern is

displayed.

FVCO must be set to encompass the incoming

frequency range.

IPUMP must be set to minimize intensity noise.

To ensure correct power-on defaults, program all regis-

ters including Test Register 0x0F, which must be set to

0x00 for normal operation. Note that unlike registers

0x00 through 0x0D, register 0x0F does not acknowl-

edge. The ACK bit remains H instead of being pulled L.

4.

5.

6.

7.

8.

9.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMU1 | TRANSISTOR | SOT-143R |

| RU101K | TRANSISTOR | SOT-23 |

| FMU3-48R000 | Logic IC |

| FMU3-48R000M | Logic IC |

| FMU3-60R000 | Logic IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMSA125 | 制造商:MicroSwitch 功能描述:4-DAY SHIPPING -Inductive |

| FMSA-461 | 制造商:INTERPOINT 制造商全稱:INTERPOINT 功能描述:EMI INPUT FILTER 28 VOLT INPUT |

| FMSA-461/883 | 制造商:INTERPOINT 制造商全稱:INTERPOINT 功能描述:EMI INPUT FILTER 28 VOLT INPUT |

| FMS-A-C0 | 制造商:Panduit Corp 功能描述: |

| FMSC1125-W | 制造商:FLORIDA MISC. 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。