- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄171235 > DSRT-L050-011 (CONEXANT SYSTEMS) SPECIALTY CONSUMER CIRCUIT, XMA PDF資料下載

參數(shù)資料

| 型號: | DSRT-L050-011 |

| 廠商: | CONEXANT SYSTEMS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, XMA |

| 文件頁數(shù): | 66/76頁 |

| 文件大小: | 632K |

| 代理商: | DSRT-L050-011 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁當(dāng)前第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

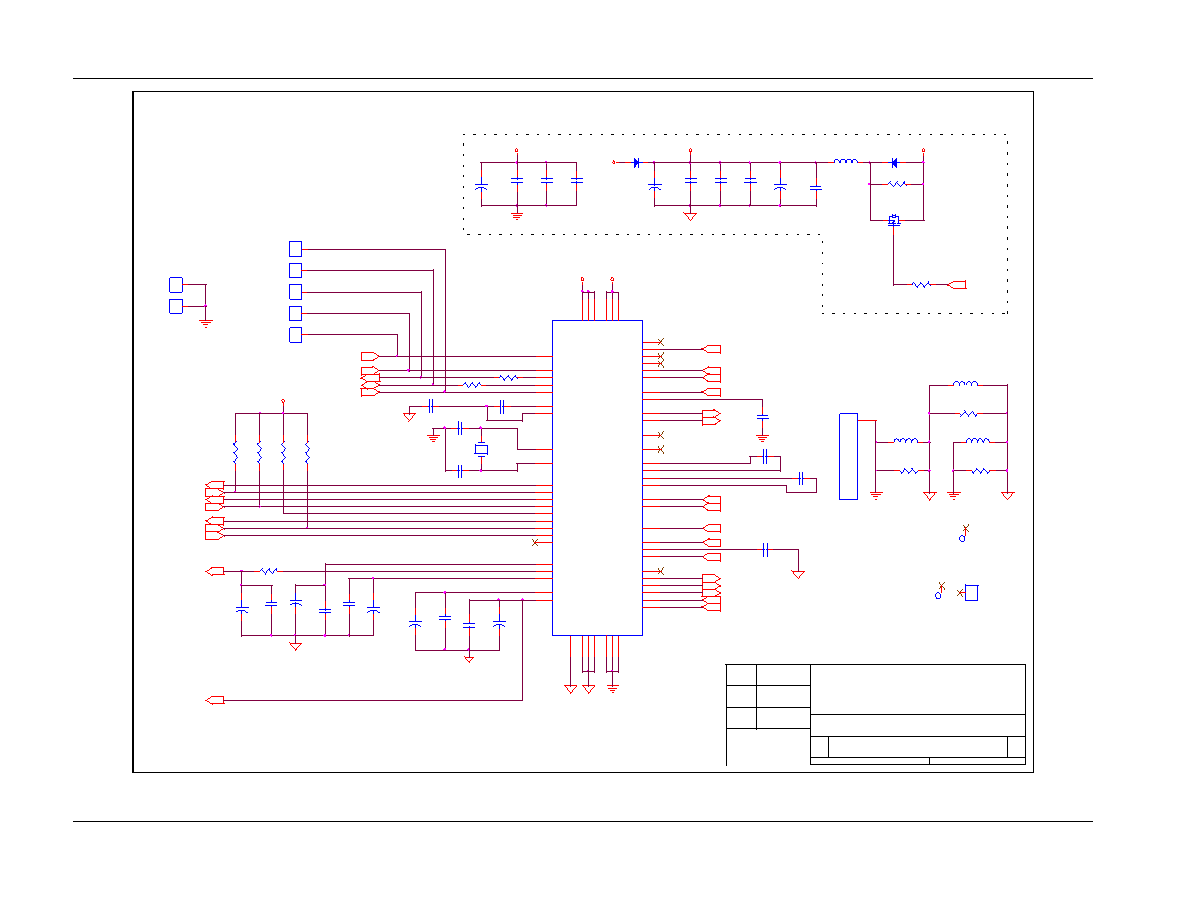

RipTide LP Audio/Comm System Product Description

1200

Conexant

69

Conexant Proprietary Information

RD00-X510

01

Riptide D7300 Refere nce Board

ROCKWEL L SEM ICO NDUCTOR SY STEM S

4311 JAMBOREE ROAD,

NEWPORT BEACH, CA 92660

B

58

Monday, November 30, 1998

Title

Size

Document Number

Rev

Date:

Sheet

of

+5VA

VCORE

+5VA

VCORE

VAUX

+5V

Brian Clark

APPD BY

ALLOWED WITHOUT PRIOR

DATE

DRN BY

DATE

NO DISSEMINATION OR USE

CHKD BY

WRITTEN PERMISSION

PROPRIETARY INFORMATION

DATE

20432

ZUMA

Screw/Washer for Bracket

Preliminary - Not For Release

Place these capacitors evenlyaround

and near 20424 Codec Device (U7).

For Layout:

AGND

MAGND

AGND

MAGND

R132, R133, R135,

R153, R154 Do Not

need to be near U2

Place caps above close to Codec (U7)

Place crystal (Y 1) and

circuitry (C105, C107)

very near Codec (U7)

MAGND

AGND

Insulator for crystal Y1

CODEC

Place E1-E5 Test Points between

Codec U7 and Riptide ASIC U4

For Layout:

GND

SYNC

BCLK

SD I

SDO

ACR#

Also, use the BOLD text to the left of the test

point as a silkscreen marking for that test point

(ex: SDO for SDATA_OUT test pin). Do this

for E1-E7.

VOICE#

LINE1_OH#

VC_M

VREF_A

LINE1_CID#

IRING#

LCS_H#

LCS_L#/RH_L#

RINGWAKE#

VREFP_M

VC_A

SY NC

BIT _CLK

SDAT A_IN

SDAT A_OUT

AC_RESET #

C98

0.1uF

C99

0.1uF

C97

0.1uF

SC1

W1

WASHER

+

C96

10uF

+

C94

10uF

C101

0.1uF

C100

0.1uF

C102

0.1uF

R45

200

C106

1uF

Y1

24.576MHz

1

2

C105

39pF

C107

39pF

C108

1uF

C77

1uF

C103

47nF

C104

12nF

R132

47K

R133

47K

R135

47K

R153

47K(omit)

C118

0.1uF

C113

0.1uF

C114

0.1uF

C111

0.1uF

R136

33

FB2

FERRIT E(om it)

R4

0

BK1

Bracket

1

R2

0

FB1

FERRIT E(om it)

FB3

FERRIT E(om it)

R15

0

ZY 1

C195

0.1uF

+

C109

10uF

+ C112

10uF

C116

0.1uF

+

C115

10uF

+

C117

10uF

+

C110

10uF

E1

1

E2

1

E3

1

E4

1

E5

1

E6

1

E7

1

R134

33

D10

1N5817

A

C

D11

1N5817(om it)

A

C

L31

10uH

300mA

R5

0(omit)

S

G

D

Q16

SI2301DS-T 1

G

D

S

R129

100

+

C25

10uF

C26

0.1uF

U7

20432-12

RXA_H

41

RXA_L1

42

TXA1_L1

47

TXA2_L1

48

TXA1_H

53

TXA2_H

54

CD_L

25

CD_GND

26

CD_R

27

MIC1

28

GPIO8/BIT _CLK2X

63

LINE_IN_L

29

LINE_IN_R

30

HP_OUT _L

51

GPIO7

62

HP_OUT _R

52

LINE_OUT _L

45

LINE_OUT _R

46

PC_BEEP

19

AUX_L

21

AUX_R

22

VIDEO_L

23

VIDEO_R

24

VREF

33

CAP2

55

VREFOUT

34

SDAT A_OUT

9

VC_A

35

CAP3

56

VREFP_M

43

GPIO4

59

VC_M

44

BIT _CLK

10

SDAT A_IN

12

RESET #

15

DV

S

S3

1

GPIO5

60

SY NC

14

GPIO0

2

DV

DD

3

64

GPIO1

3

GPIO6

61

GPIO2

4

DV

S

S1

8

GPIO3

58

AV

SS

1

17

AV

SS

4

20

DV

S

S2

11

AV

SS

2

32

AV

SS

3

40

CID_INBIT

57

DV

DD

1

5

AV

D

D1

16

AV

D

D2

31

AV

D

D3

49

EAPD

18

DV

DD

2

13

XT LI

6

XTLO

7

MIX_CIN_L

36

MIX_COUT _L

37

MIX_CIN_R

38

MIX_COUT _R

39

MONO_OUT /POR

50

VREFOUT

TXA2_L1

TXA1_L1

RXA_L1

TELIN

TELOUT

VOICE#

LOUT _L

MIC1

LINE1_OH#

LCS_L#/RH_L#

AUX_R

CD_L

LINE_L

IRING#

LOUT _R

CD_R

AUX_L

LCS_H#

VC_M

LINE_R

PC_BEEP

LINE1_CID#

AC_RESET #

SY NC

SDAT A_OUT

BIT _CLK

CID_INBIT

SDAT A_IN

RINGWAKE#

VPCIEN#

)LJXUH 5LS7LGH 5HIHUHQFH 'HVLJQ 6FKHPDWLF 3 $XGLR&RPP &RQQHFWRU ,QWHUIDFH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSS710D223S12-22 | 1 FUNCTIONS, 12 V, 7 A, DATA LINE FILTER |

| DST9HB32E101Q55J | 1 FUNCTIONS, 250 V, 6 A, DATA LINE FILTER |

| DST9HB32E220Q55J | 1 FUNCTIONS, 250 V, 6 A, DATA LINE FILTER |

| DST9HB32E222Q55J | 1 FUNCTIONS, 250 V, 6 A, DATA LINE FILTER |

| DST9HB32E271Q55J | 1 FUNCTIONS, 250 V, 6 A, DATA LINE FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSR-TSS-S1 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-S2 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-ST2-1 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-T1 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-T2 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。